Мультимедийная презентация для дисциплины «Информатика»

Литература

- Толстобров А.П. Архитектура ЭВМ. – Учебные материалы для студентов 1-го курса физического факультета и факультета компьютерных наук. Воронеж: ВГУ, 2016. №496. – 93 с.

- Архитектура ЭВМ: Справочные материалы для проведения практических занятий /Сост. А.П.Толстобров, А.М.Воробьев, А.В.Сычев. – Воронеж: ВГУ, 201 5. – № 670. – 54 с.

- В.Л.Бройдо, О.П.Ильина. Архитектура ЭВМ и систем: Учебник для вузов. – СПб.: Питер, 2016. – 718 с.: ил.

- Столлингс Вильям. Структурная организация и архитектура компьютерных систем, 5-е изд.: Пер. с англ. – М. : Изд. дом «Вильямс», 20015. – 896 с.

- Танненбаум Э. Архитектура компьютера. – СПб.: Питер, 2016. – 704 с.: ил.

Архитектура ЭВМ

- Термин архитектура компьютерной системы относится к тем характеристикам системы, которые доступны извне , т.е. со стороны программы , или оказывают непосредственное влияние на логику выполнения программы

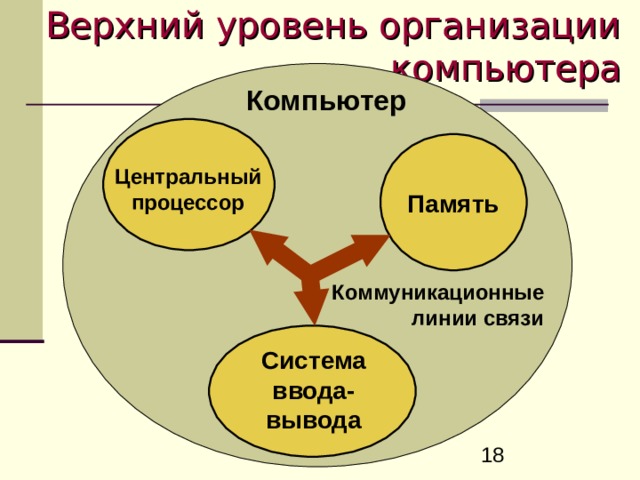

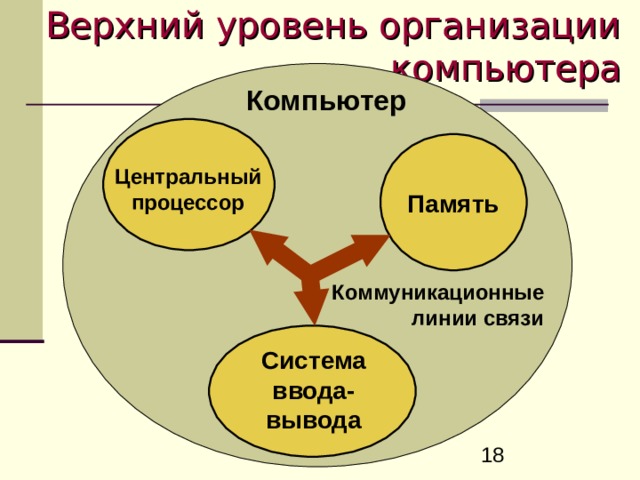

Верхний уровень организации компьютера

Компьютер

Центральный

процессор

Память

Коммуникационные

линии связи

Система

ввода-

вывода

Фон-неймановские принципы организации ЭВМ

- В 1946 году Джон фон-Нейман вместе с группой работавших вместе с ним американских ученых сформулировал основные принципы, которым должно удовлетворять устройство, получившее название электронная вычислительная машина ( ЭВМ ) или компьютер .

Фон-неймановские принципы организации ЭВМ

- Компьютер – это машина с хранимой программой

- Выполняемые компьютером команды и операнды представлены в ЭВМ в виде двоичного кода с определенным количеством разрядов

- Память ЭВМ организована в виде последовательности запоминающих ячеек , в каждой из которых может храниться (запоминаться) некоторый двоичный код. В конкретный момент времени можно обратиться для записи или чтения к любой одной из этих ячеек независимо от ее расположения в памяти , указав адрес (порядковый номер) этой ячейки.

Фон-неймановские принципы организации ЭВМ

- Для хранения команд и данных в компьютере используется одна и та же общая память

- В двоичных кодах команд и данных отсутствуют какие либо признаки, позволяющие явно отличать их друг от друга

- Предназначение данных , их тип и способ использования также явно в их коде не указываются

- В классическом фон-неймановском компьютере используется один центральный процессор

Фон-неймановские принципы организации ЭВМ

Компьютер – это машина с хранимой программой

- Компьютер – это машина с хранимой программой

- Компьютер работает по программе

- Любая выполняемая компьютером задача представляется в виде последовательности достаточно простых действий , реализуемых с помощью соответствующих команд

- Любая выполняемая компьютером задача представляется в виде последовательности достаточно простых действий , реализуемых с помощью соответствующих команд

- Команда – это закодированная инструкция для выполнения элементарной операции ЭВМ

- Команда – это закодированная инструкция для выполнения элементарной операции ЭВМ

- Программа – это последовательность команд , которые должен выполнять компьютер,

- Программа – это последовательность команд , которые должен выполнять компьютер,

причем,

если не задано иного, то всегда выполняется следующая по-порядку команда

- причем, если не задано иного, то всегда выполняется следующая по-порядку команда

- Компьютер – это машина с хранимой программой

- Команды, составляющие программу должны храниться (запоминаться) в предназначенном для этого устройстве, из которого эти команды должны быстро извлекаться и передаваться в процессор компьютера для исполнения

- Иными словами, в составе компьютера должно быть специальное запоминающее устройство ( внутренняя память ) для записи кодов команд программы

- Представление команд и данных

- Выбор способа кодирования команд и данных

- Выполняемые компьютером команды и данные , т.е. операнды, над которыми выполняются задаваемые командами операции, представлены в компьютере в виде двоичного кода с определенным количеством разрядов

- Выполняемые компьютером команды и данные , т.е. операнды, над которыми выполняются задаваемые командами операции, представлены в компьютере в виде двоичного кода с определенным количеством разрядов

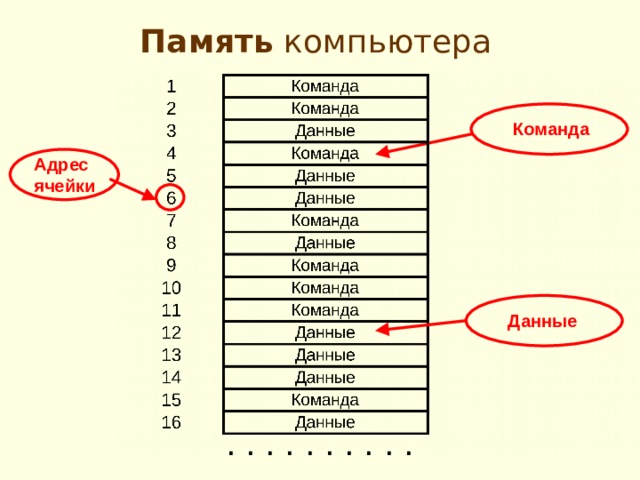

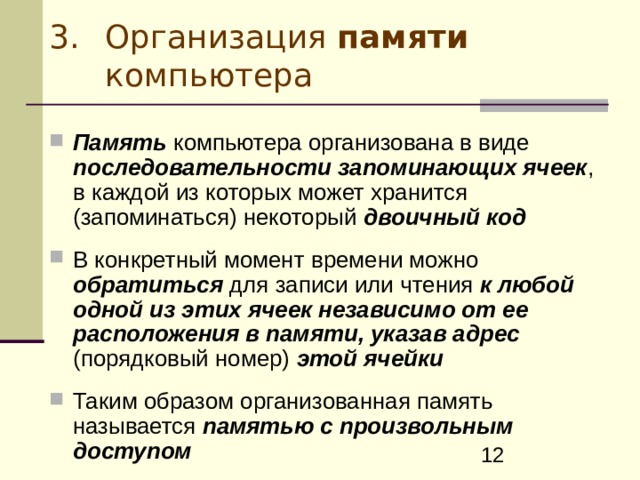

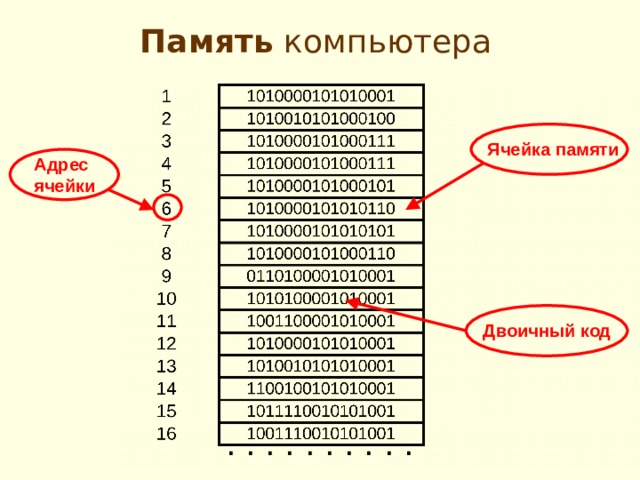

- Организация памяти компьютера

- Память компьютера организована в виде последовательности запоминающих ячеек , в каждой из которых может хранится (запоминаться) некоторый двоичный код

- В конкретный момент времени можно обратиться для записи или чтения к любой одной из этих ячеек независимо от ее расположения в памяти, указав адрес (порядковый номер) этой ячейки

- Таким образом организованная память называется памятью с произвольным доступом

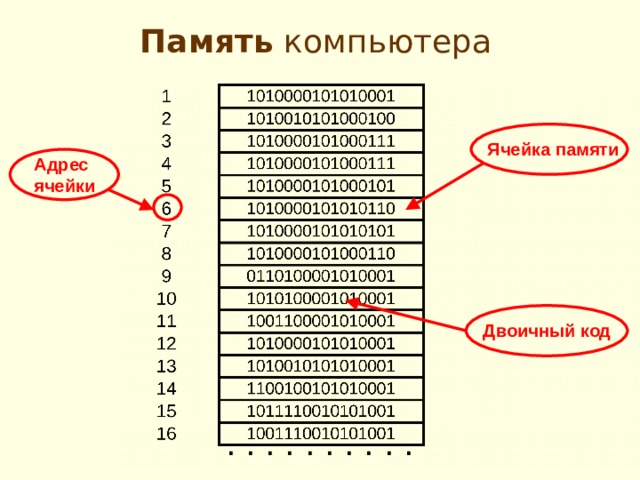

Память компьютера

Ячейка памяти

Адрес

ячейки

Двоичный код

. . . . . . . . . .

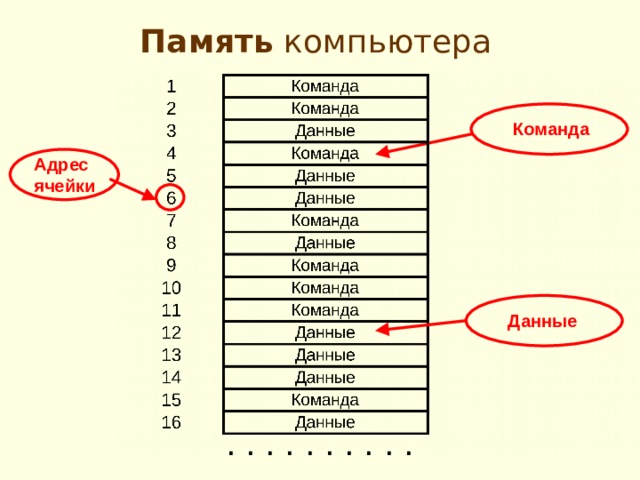

- Для хранения данных и хранения команд в компьютере используется одна и та же общая память

Память компьютера

Команда

Адрес

ячейки

Данные

. . . . . . . . . .

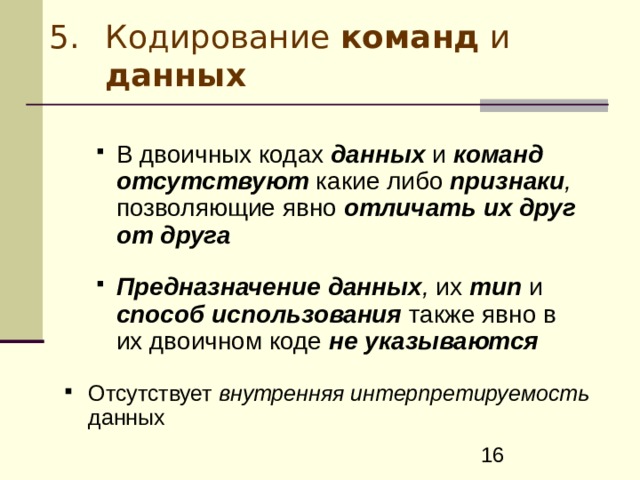

- Кодирование команд и данных

- В двоичных кодах данных и команд отсутствуют какие либо признаки , позволяющие явно отличать их друг от друга Предназначение данных , их тип и способ использования также явно в их двоичном коде не указываются

- В двоичных кодах данных и команд отсутствуют какие либо признаки , позволяющие явно отличать их друг от друга

- Предназначение данных , их тип и способ использования также явно в их двоичном коде не указываются

- Отсутствует внутренняя интерпретируемость данных

- Выполнение операций (команд)

- В классическом фон-неймановском компьютере используется один центральный процессор

Верхний уровень организации компьютера

Компьютер

Центральный

процессор

Память

Коммуникационные

линии связи

Система

ввода-

вывода

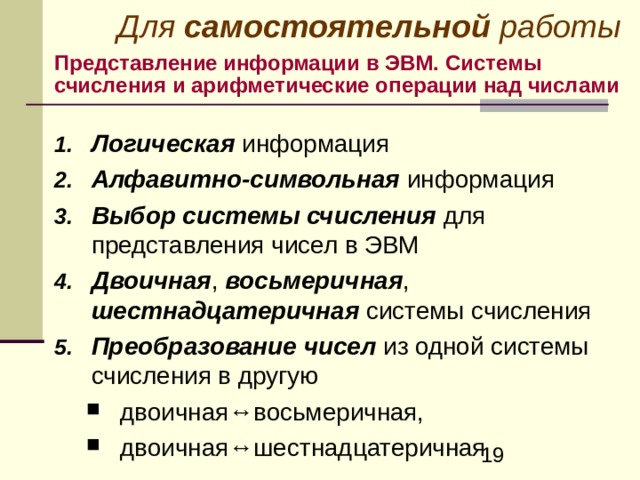

Для самостоятельной работы

Представление информации в ЭВМ. Системы счисления и арифметические операции над числами

- Логическая информация

- Алфавитно-символьная информация

- Выбор системы счисления для представления чисел в ЭВМ

- Двоичная , восьмеричная , шестнадцатеричная системы счисления

- Преобразование чисел из одной системы счисления в другую

- двоичная ↔ восьмеричная, двоичная ↔ шестнадцатеричная

- двоичная ↔ восьмеричная,

- двоичная ↔ шестнадцатеричная

Для самостоятельной работы

Представление информации в ЭВМ. Системы счисления и арифметические операции над числами

- Представление в ЭВМ целых двоичных чисел без знака

- Представление в ЭВМ целых чисел со знаком

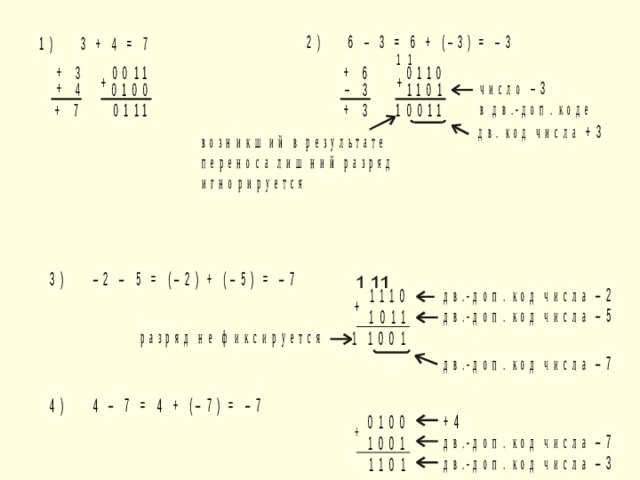

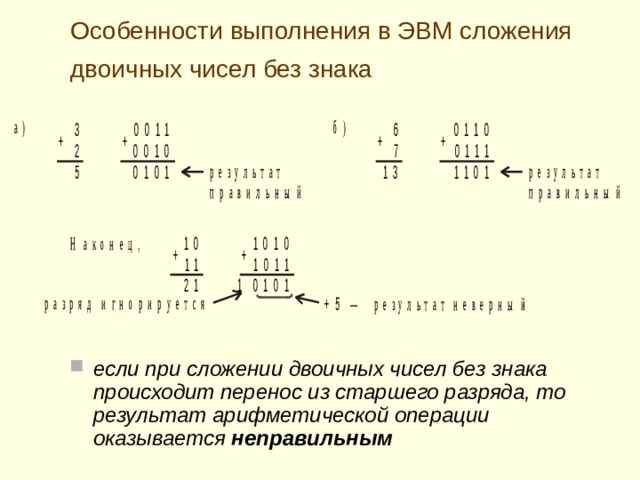

- Особенности выполнения в ЭВМ операции сложения двоичных чисел без знака

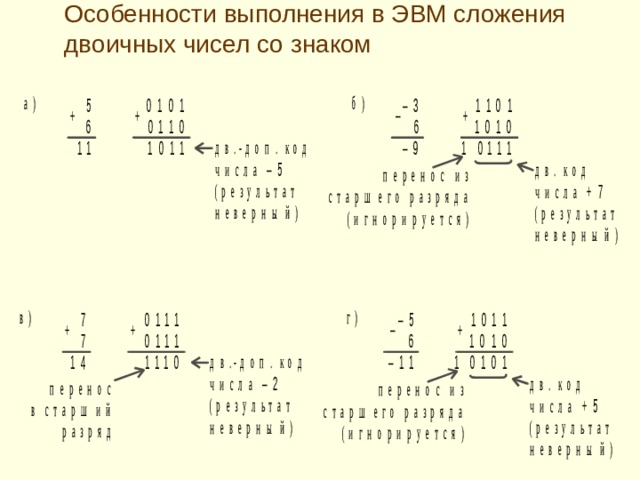

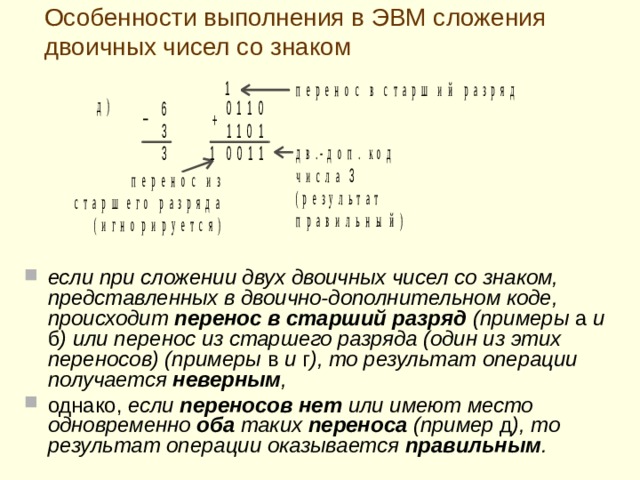

- Особенности выполнения в ЭВМ операции сложения двоичных чисел со знаком

Представление информации в ЭВМ. Системы счисления и арифметические операции над числами

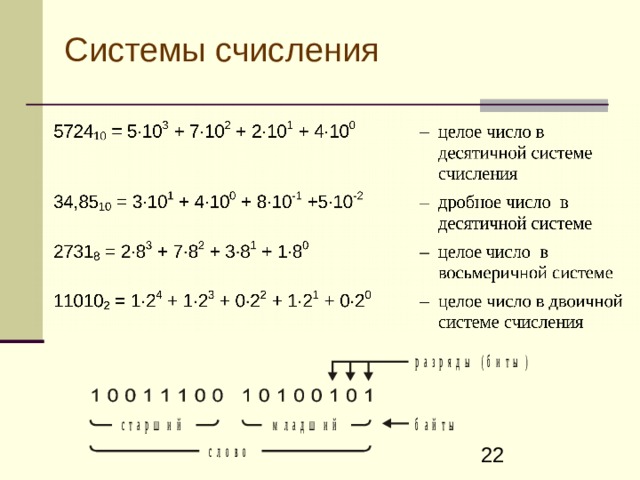

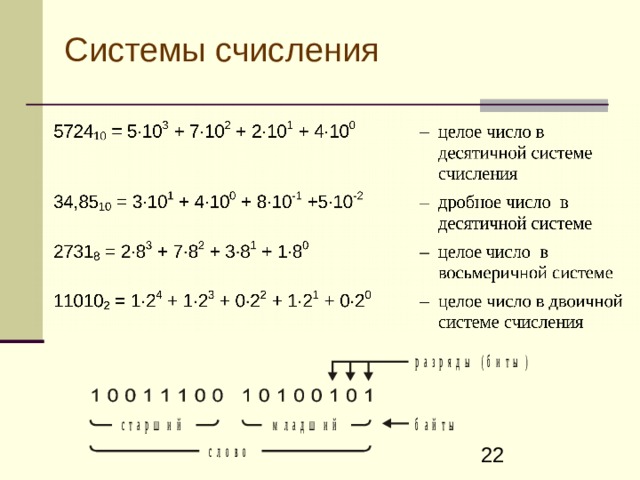

Системы счисления

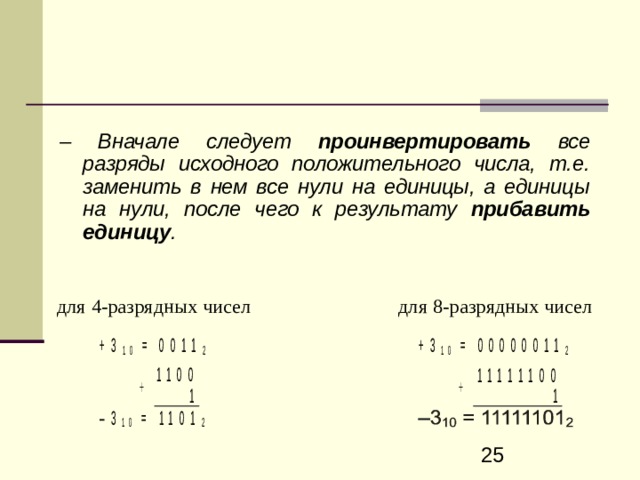

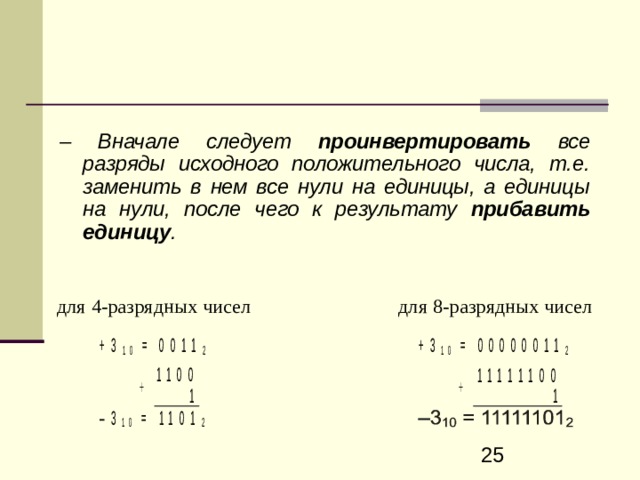

– Вначале следует проинвертировать все разряды исходного положительного числа, т.е. заменить в нем все нули на единицы, а единицы на нули, после чего к результату прибавить единицу .

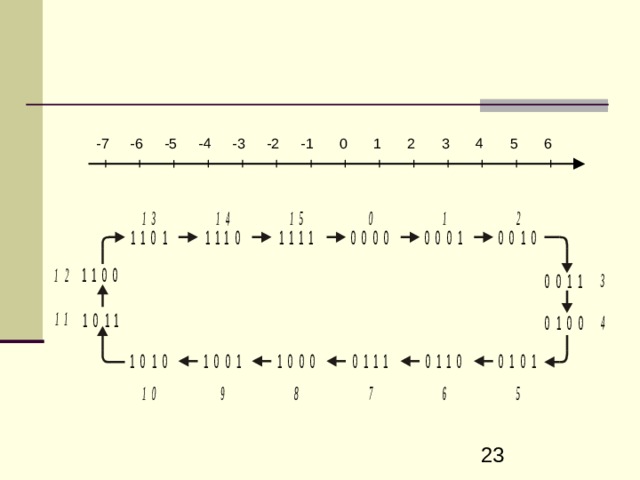

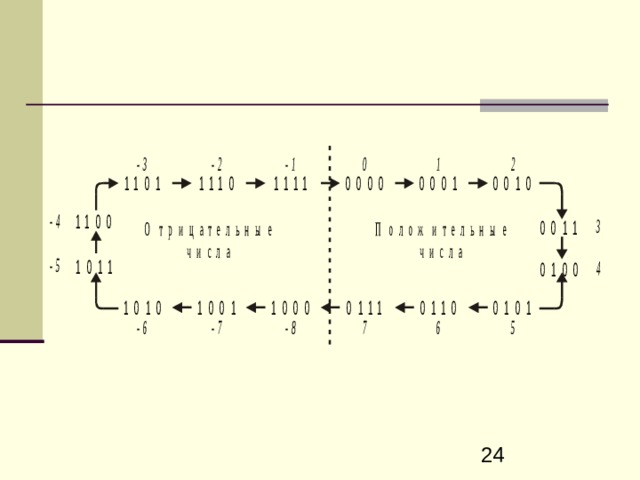

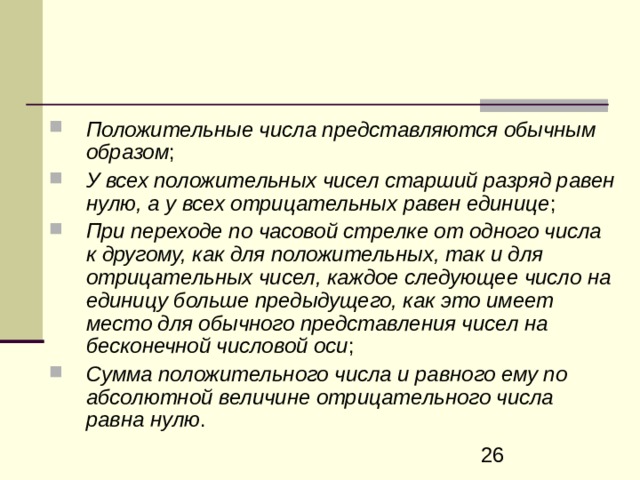

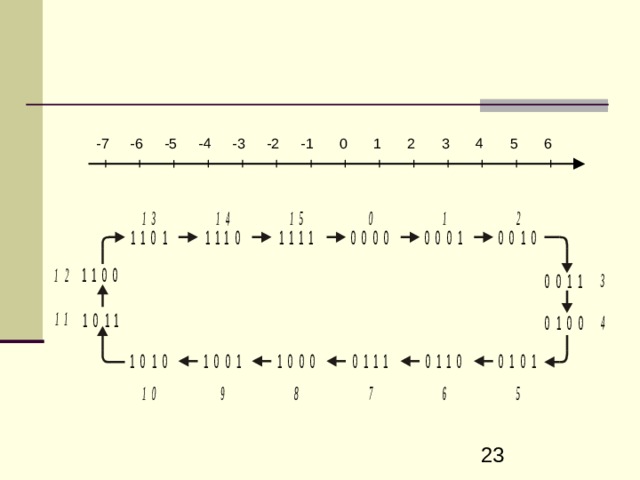

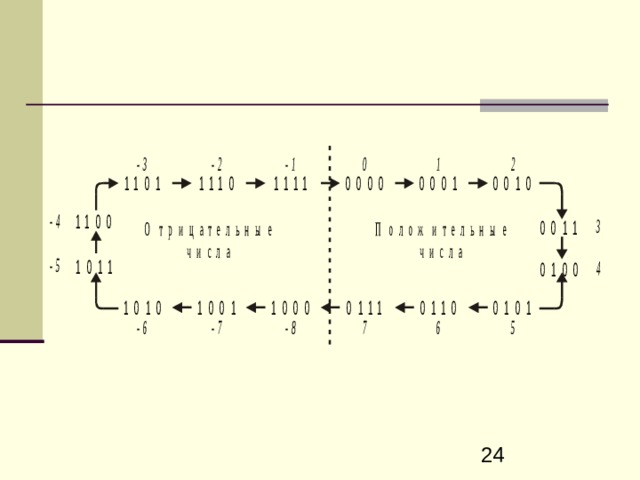

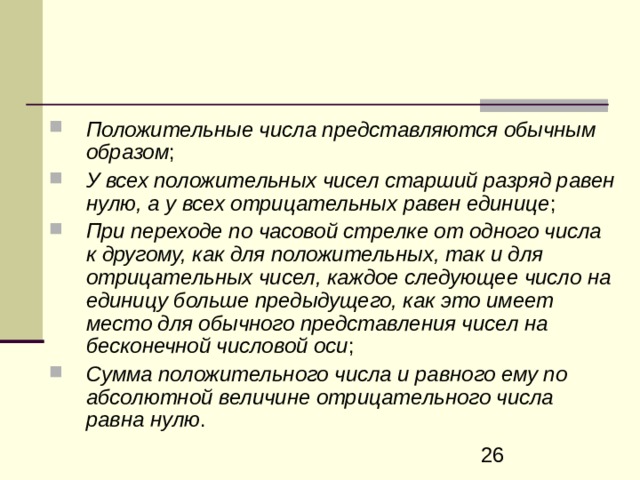

- Положительные числа представляются обычным образом ;

- У всех положительных чисел старший разряд равен нулю, а у всех отрицательных равен единице ;

- При переходе по часовой стрелке от одного числа к другому, как для положительных, так и для отрицательных чисел, каждое следующее число на единицу больше предыдущего, как это имеет место для обычного представления чисел на бесконечной числовой оси ;

- Сумма положительного числа и равного ему по абсолютной величине отрицательного числа равна нулю .

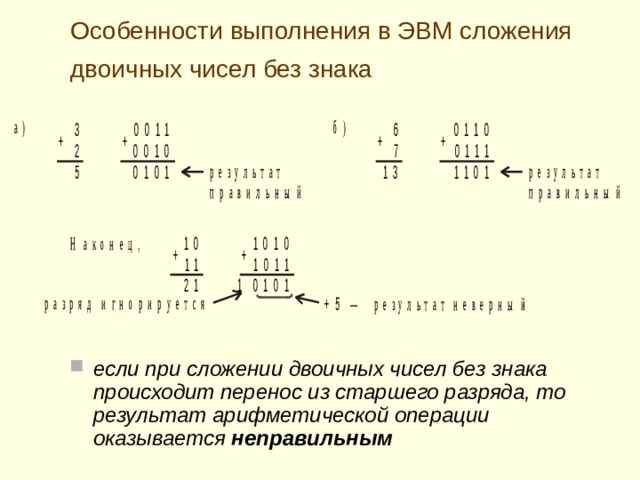

Особенности выполнения в ЭВМ сложения двоичных чисел без знака

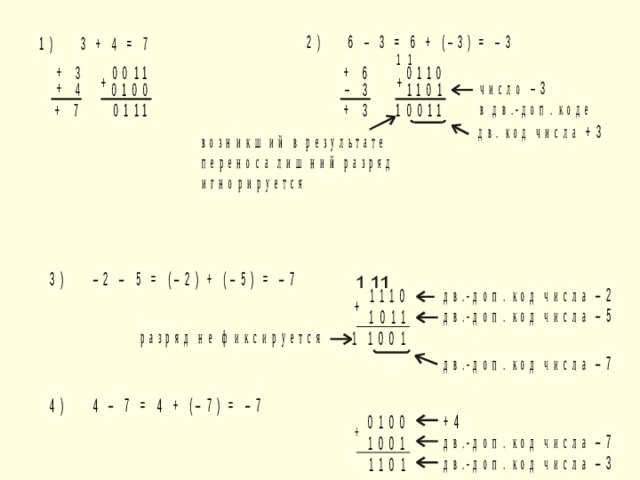

- если при сложении двоичных чисел без знака происходит перенос из старшего разряда, то результат арифметической операции оказывается неправильным

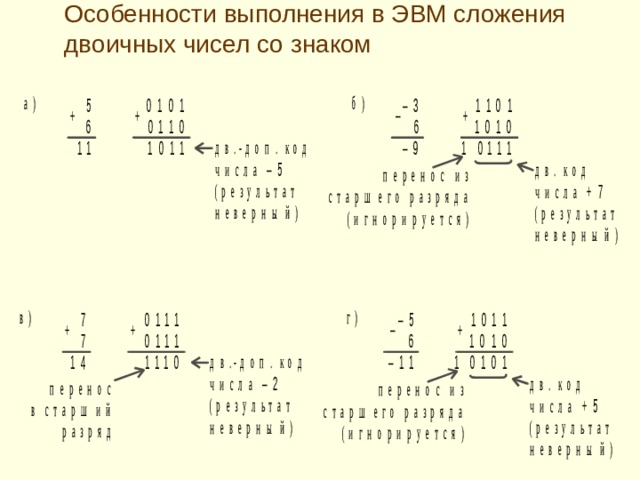

Особенности выполнения в ЭВМ сложения двоичных чисел со знак ом

Особенности выполнения в ЭВМ сложения двоичных чисел со знак ом

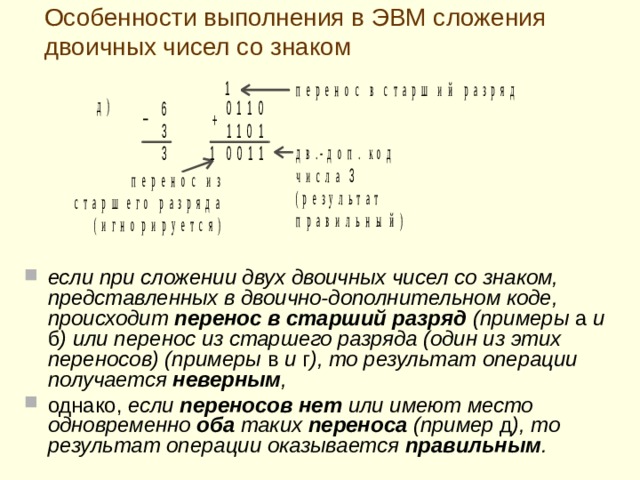

- если при сложении двух двоичных чисел со знаком, представленных в двоично-дополнительном коде, происходит перенос в старший разряд (примеры а и б ) или перенос из старшего разряда (один из этих переносов) (примеры в и г ), то результат операции получается неверным ,

- однако, если переносов нет или имеют место одновременно оба таких переноса (пример д ), то результат операции оказывается правильным .

Принципы построения цифровых устройств для выполнения логических и арифметических операций над двоичными числами

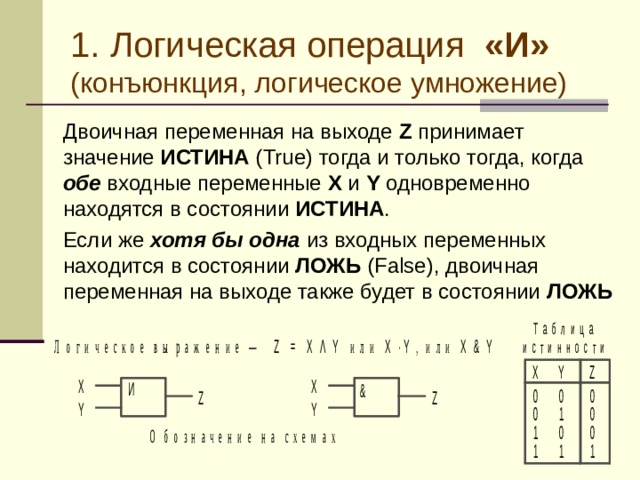

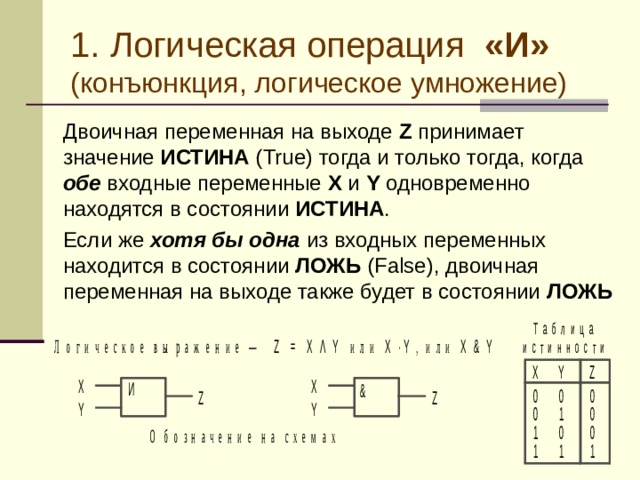

1. Логическая операция «И» (конъюнкция, логическое умножение)

Двоичная переменная на выходе Z принимает значение ИСТИНА (True) тогда и только тогда, когда обе входные переменные X и Y одновременно находятся в состоянии ИСТИНА .

Если же хотя бы одна из входных переменных находится в состоянии ЛОЖЬ (False), двоичная переменная на выходе также будет в состоянии ЛОЖЬ

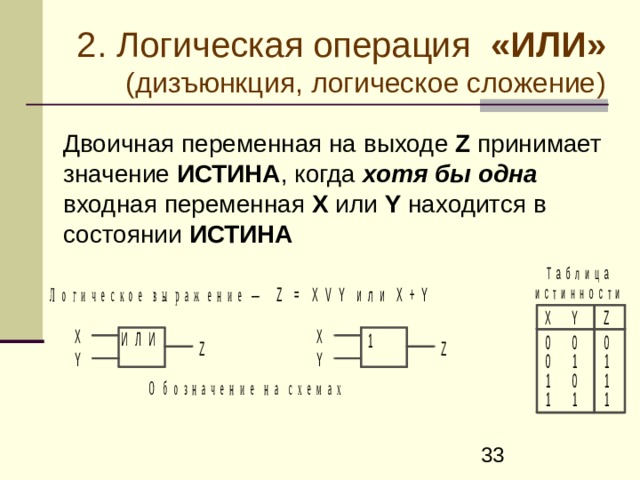

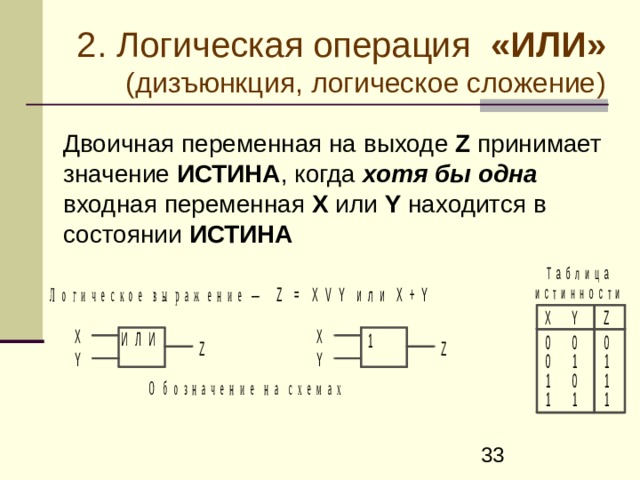

2. Логическая операция «ИЛИ» ( дизъюнкция, логическое сложение )

Двоичная переменная на выходе Z принимает значение ИСТИНА , когда хотя бы одна входная переменная X или Y находится в состоянии ИСТИНА

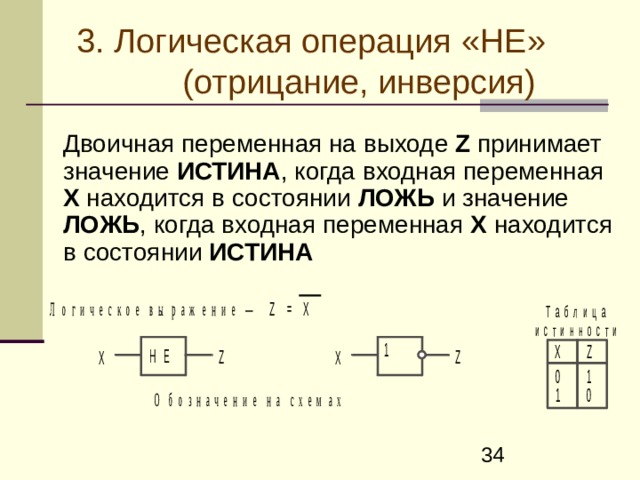

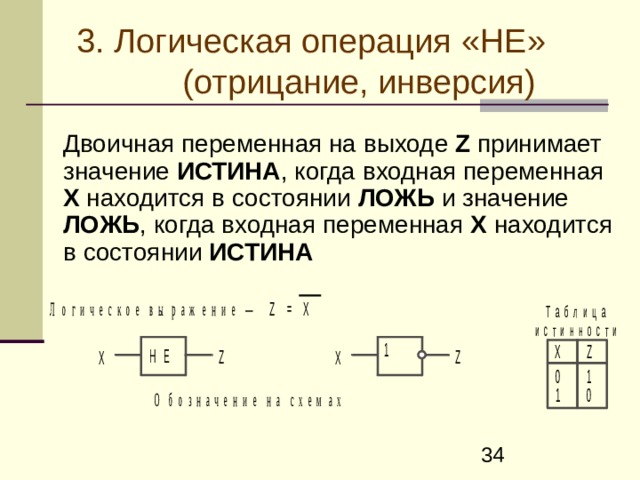

3. Логическая операция « НЕ » (отрицание, инверсия)

Двоичная переменная на выходе Z принимает значение ИСТИНА , когда входная переменная X находится в состоянии ЛОЖЬ и значение ЛОЖЬ , когда входная переменная X находится в состоянии ИСТИНА

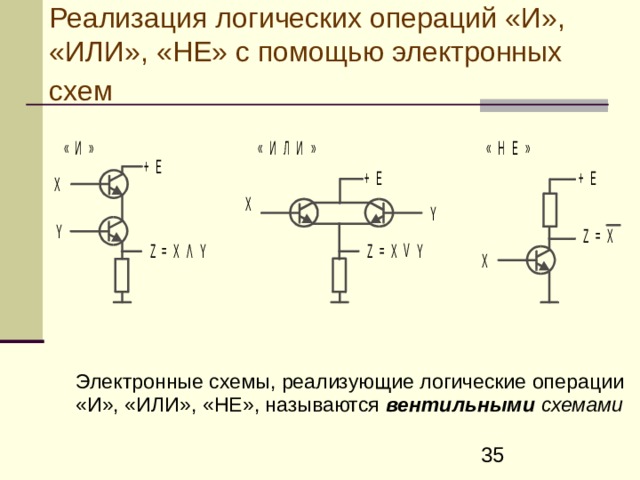

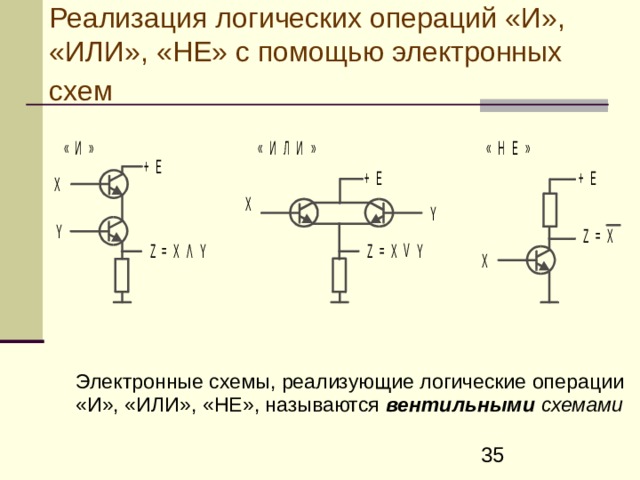

Реализация л огически х операци й « И » , « ИЛИ » , « НЕ » с помощью электронных схем

Электронные схемы, реализующие логические операции « И » , « ИЛИ » , « НЕ » , называются вентильными схемами

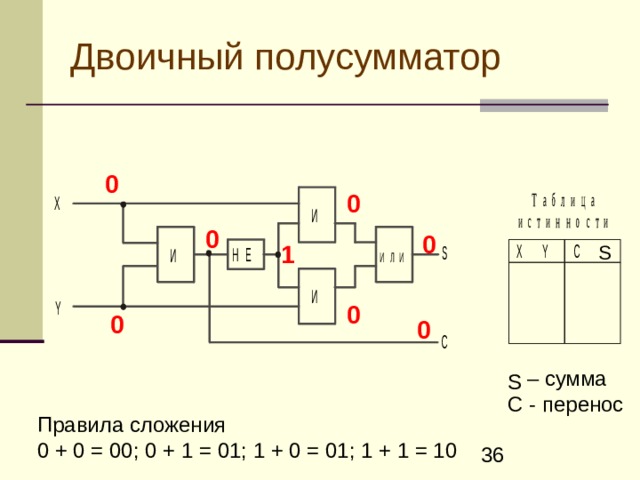

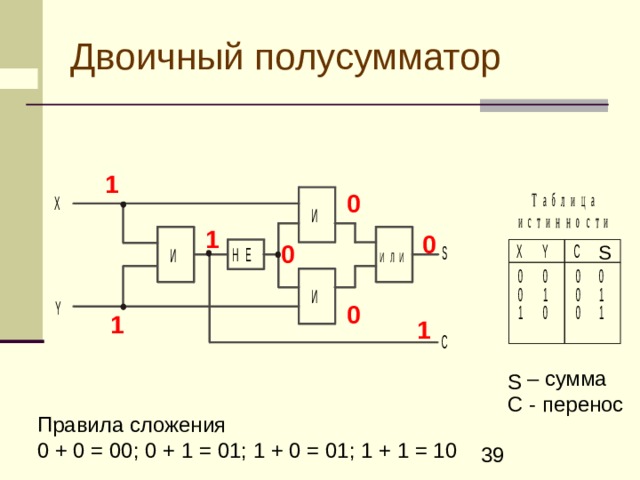

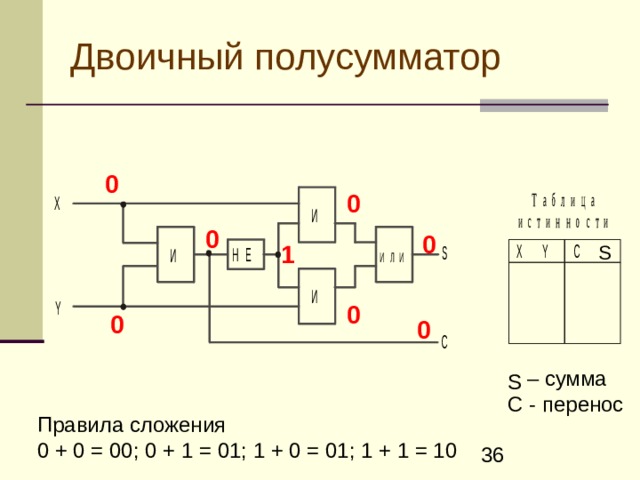

Двоичный полусумматор

0

0

0

0

1

S

0

0

0

Z – сумма

C - перенос

S

Правила сложения

0 + 0 = 00; 0 + 1 = 01; 1 + 0 = 01; 1 + 1 = 10

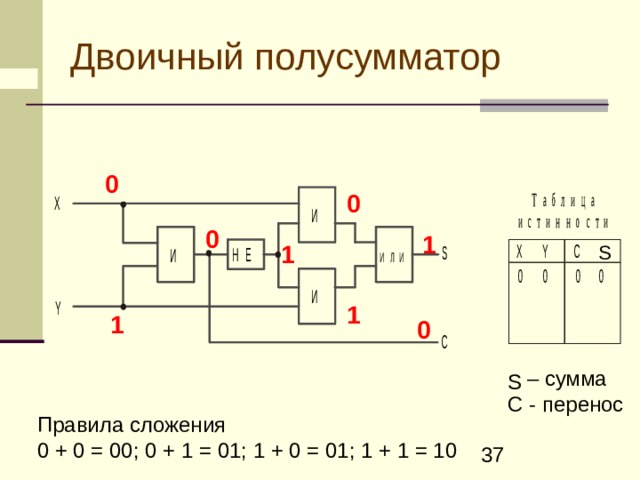

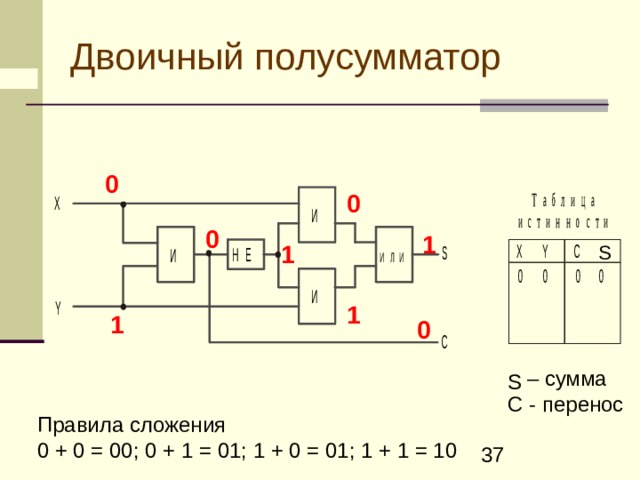

Двоичный полусумматор

0

0

0

1

1

S

1

1

0

Z – сумма

C - перенос

S

Правила сложения

0 + 0 = 00; 0 + 1 = 01; 1 + 0 = 01; 1 + 1 = 10

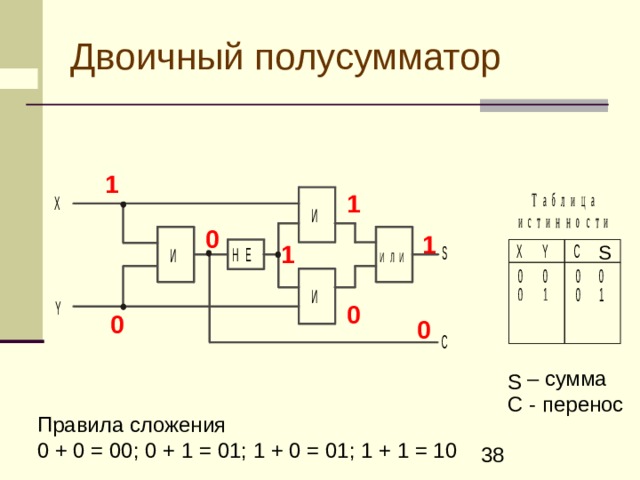

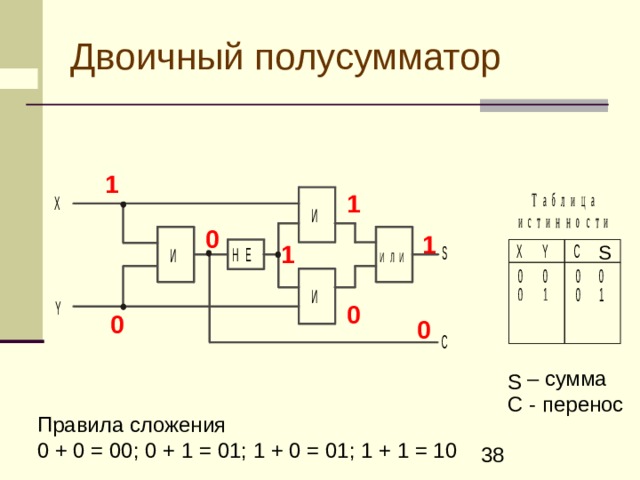

Двоичный полусумматор

1

1

0

1

1

S

0

0

0

Z – сумма

C - перенос

S

Правила сложения

0 + 0 = 00; 0 + 1 = 01; 1 + 0 = 01; 1 + 1 = 10

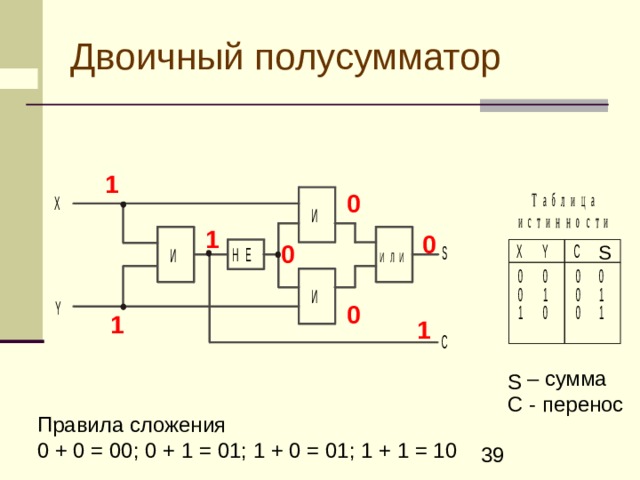

Двоичный полусумматор

1

0

1

0

0

S

0

1

1

Z – сумма

C - перенос

S

Правила сложения

0 + 0 = 00; 0 + 1 = 01; 1 + 0 = 01; 1 + 1 = 10

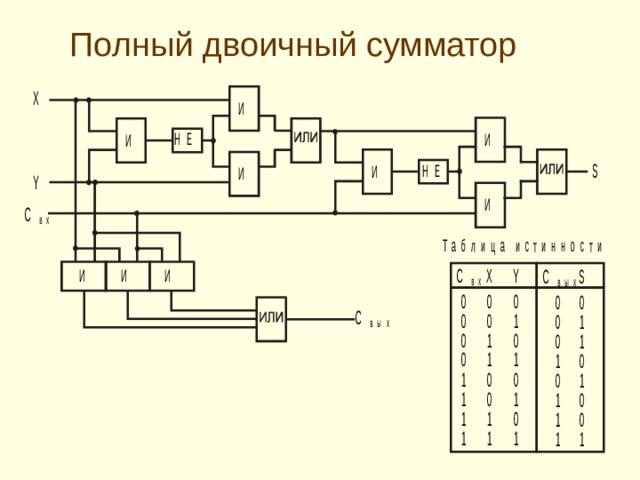

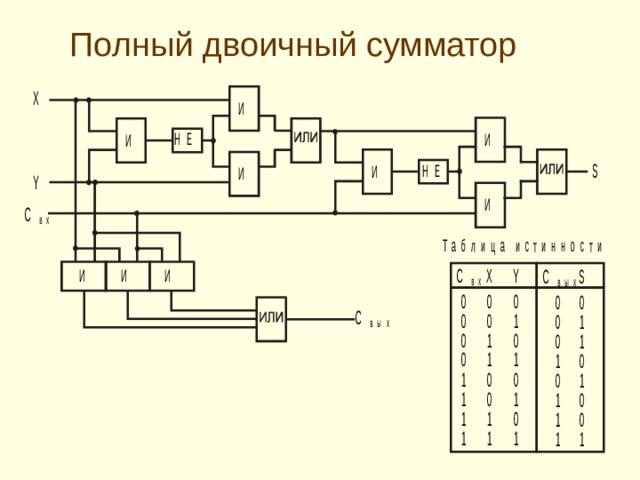

Полный двоичный сумматор

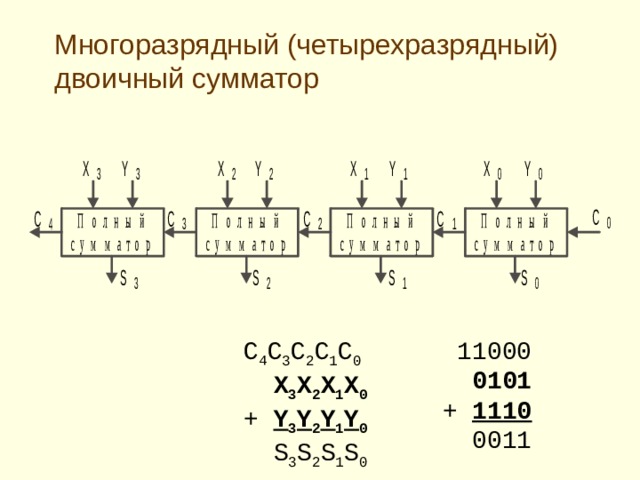

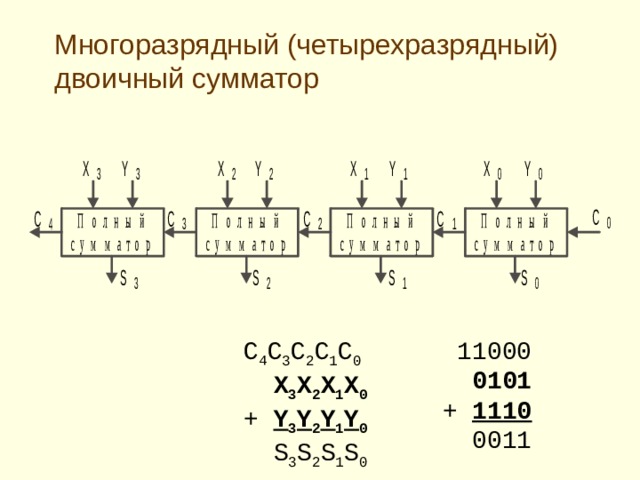

Многоразрядный (четырехразрядный) двоичный сумматор

C 4 C 3 C 2 C 1 C 0

X 3 X 2 X 1 X 0

+ Y 3 Y 2 Y 1 Y 0

S 3 S 2 S 1 S 0

11000

0101

+ 1110

0011

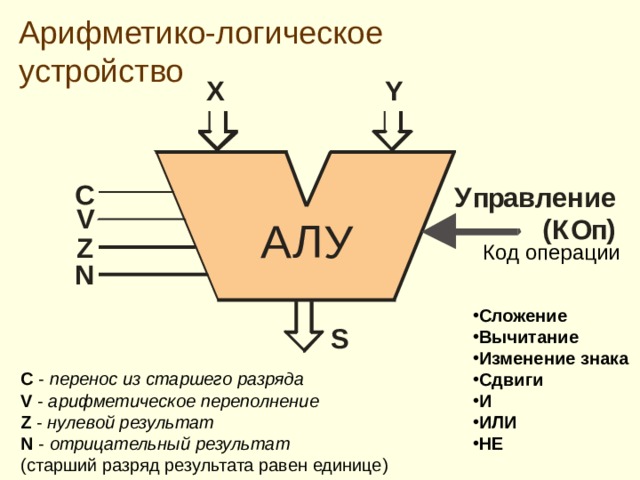

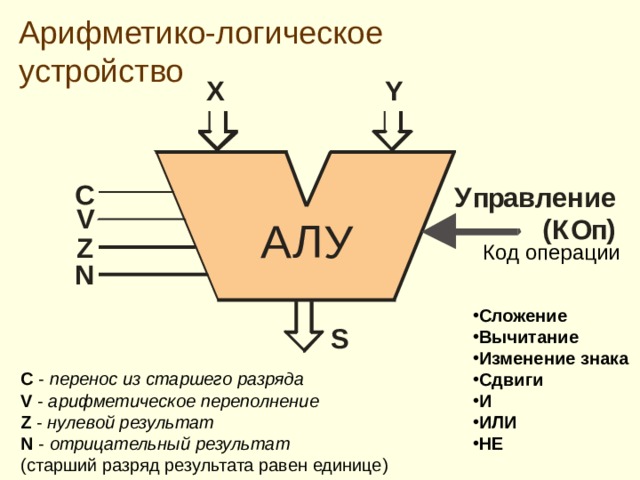

Арифметико-логическое устройство

Код операции

- Сложение

- Вычитание

- Изменение знака

- Сдвиги

- И

- ИЛИ

- НЕ

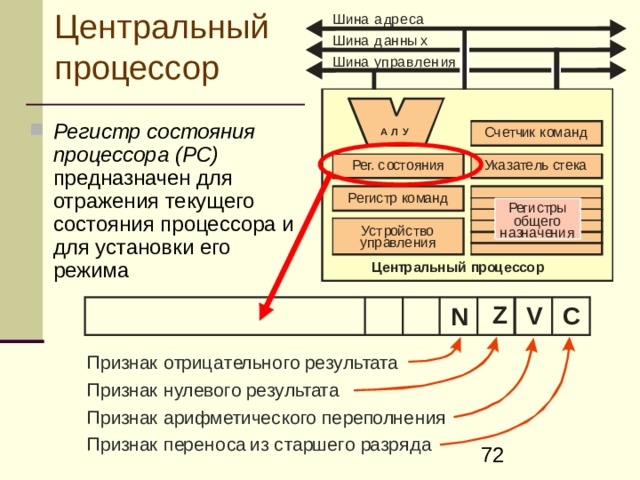

C - перенос из старшего разряда

V - арифметическое переполнение

Z - нулевой результат

N - отрицательн ый результат

(старший разряд результата равен единице)

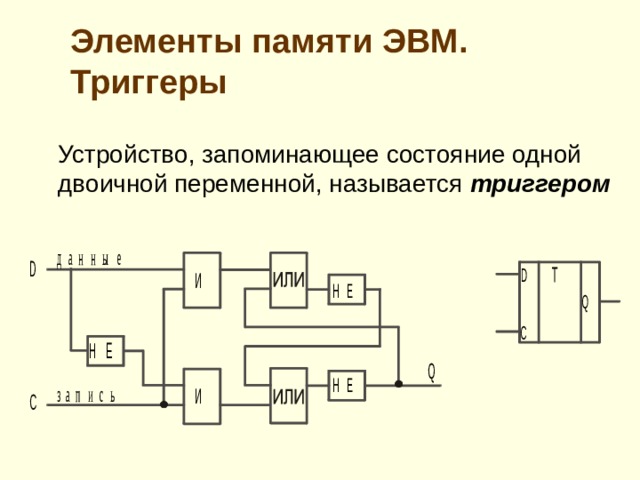

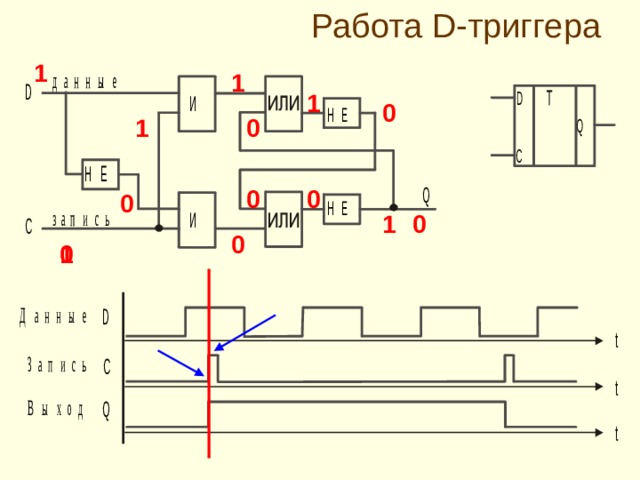

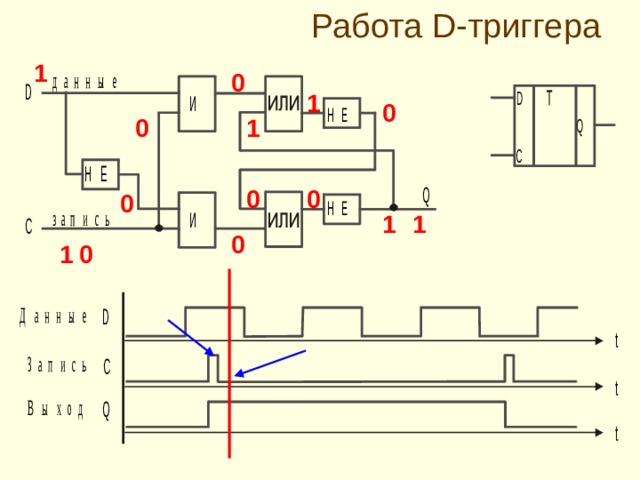

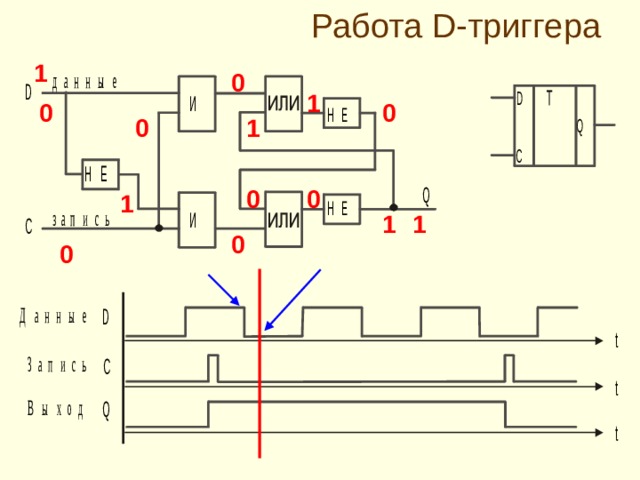

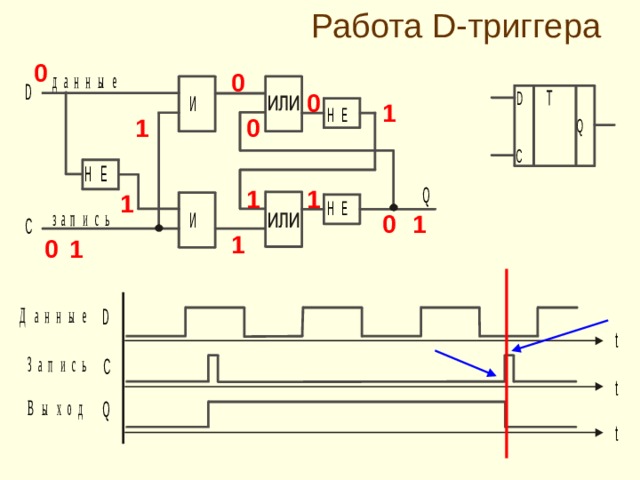

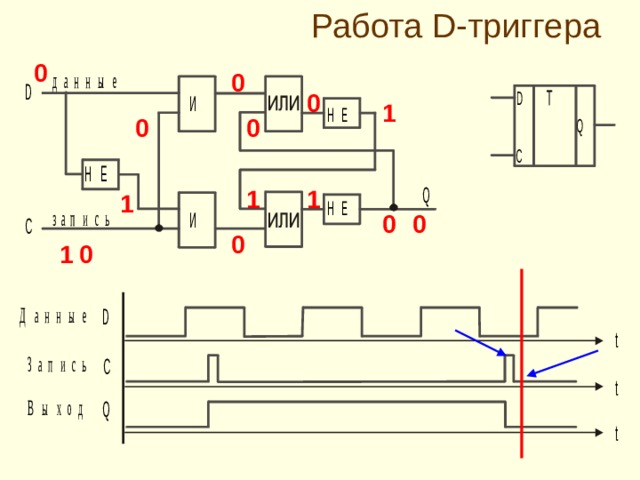

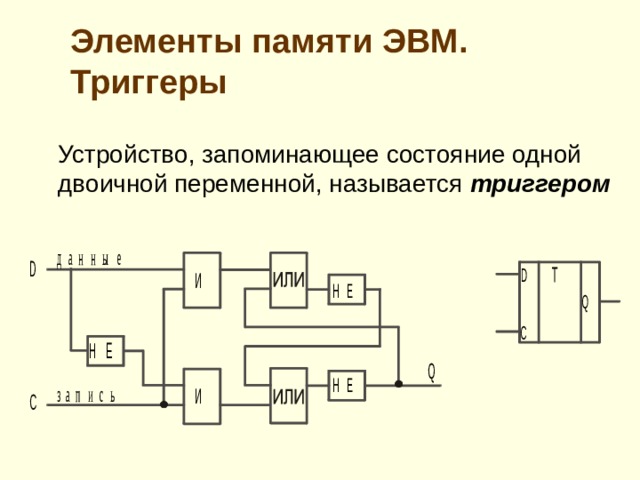

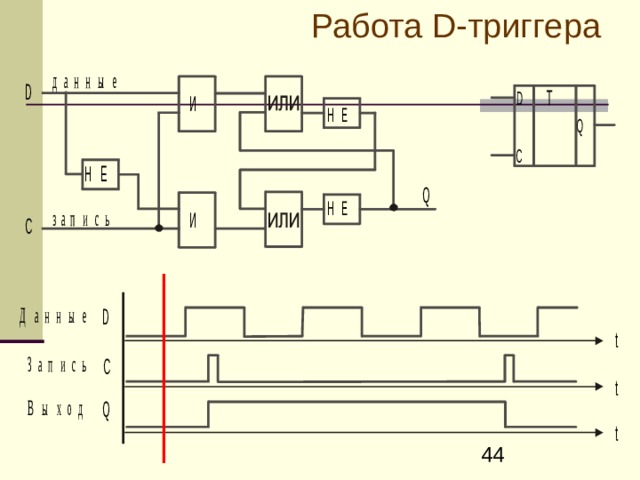

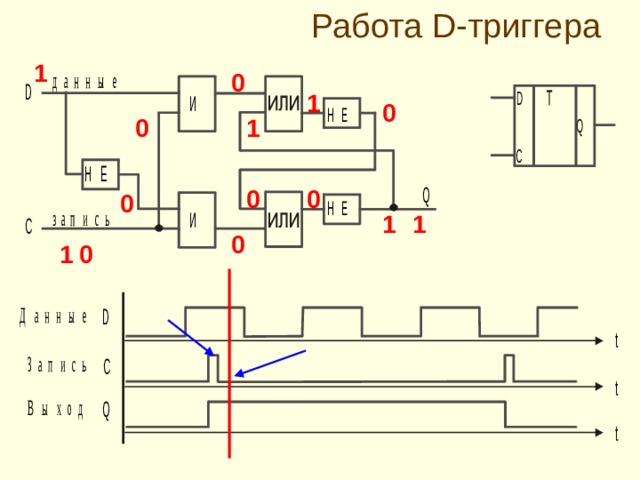

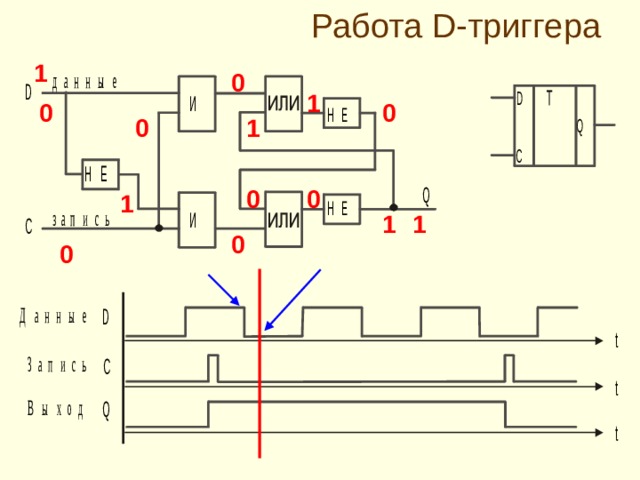

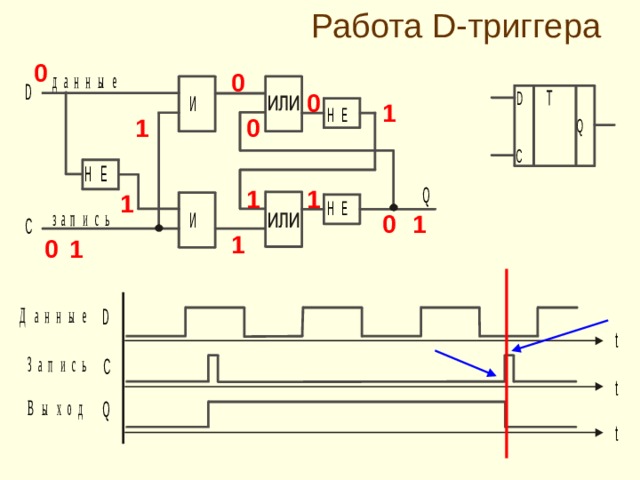

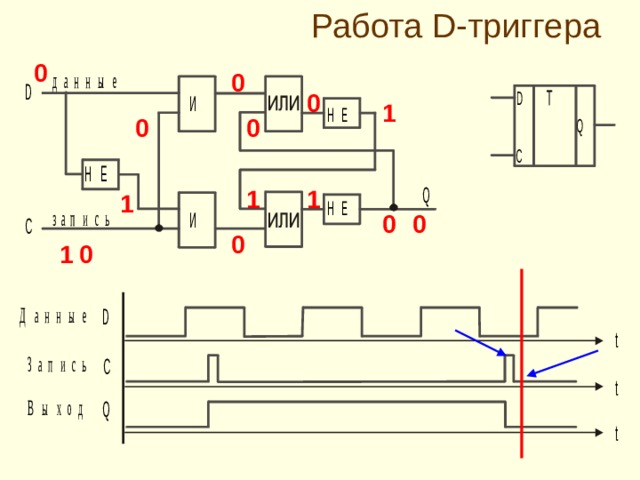

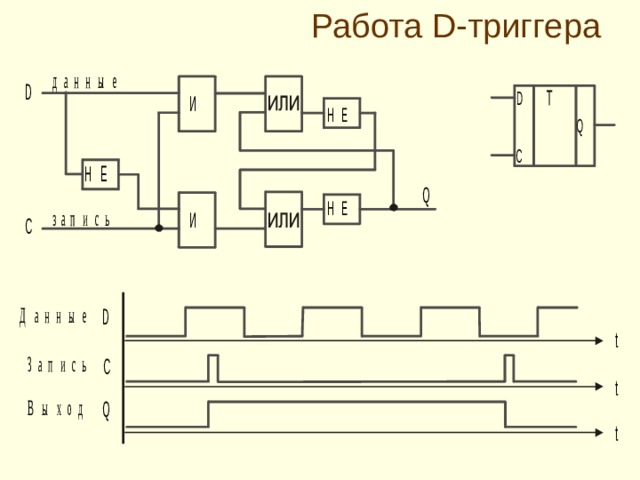

Элементы памяти ЭВМ. Триггеры

Устройство, запоминающее состояние одной двоичной переменной, называется триггером

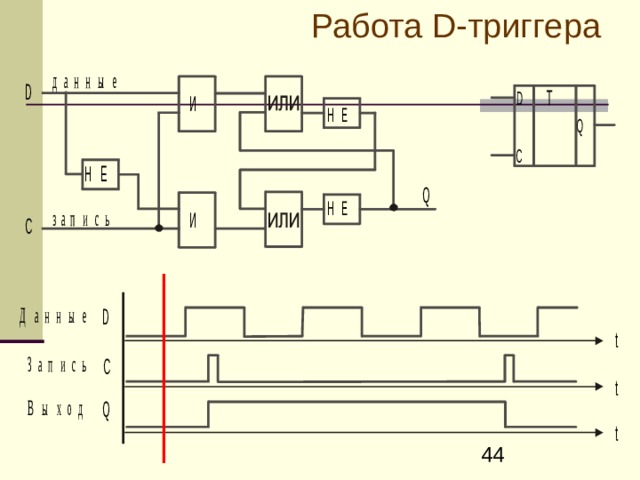

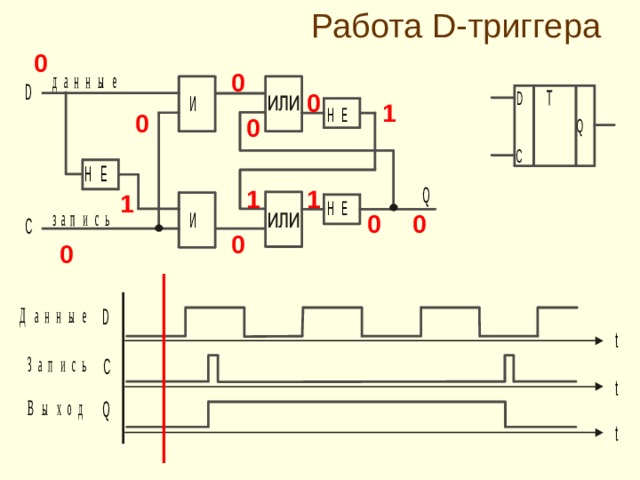

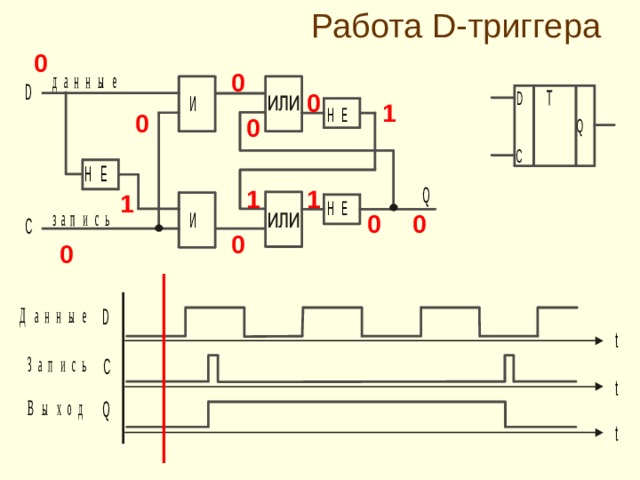

Работа D- триггера

Работа D- триггера

0

0

0

1

0

0

1

1

1

0

0

0

0

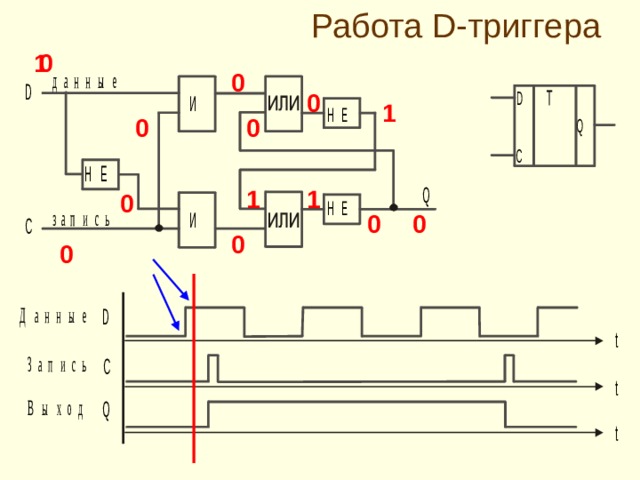

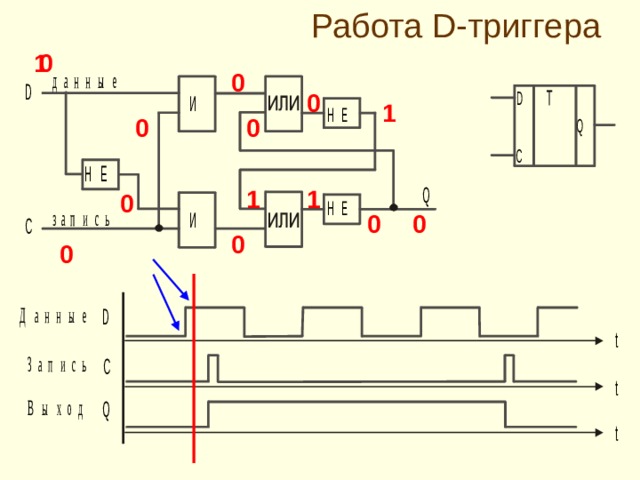

Работа D- триггера

1

0

0

0

1

0

0

1

1

0

0

0

0

0

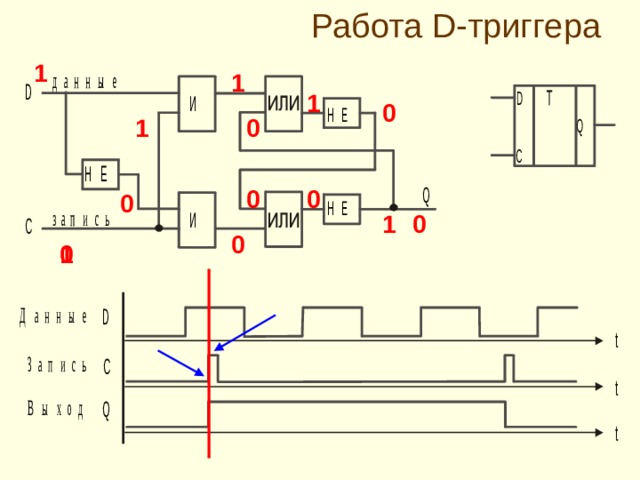

Работа D- триггера

1

1

1

0

0

1

0

0

0

0

1

0

1

0

Работа D- триггера

1

0

1

0

1

0

0

0

0

1

1

0

0

1

Работа D- триггера

1

0

1

0

0

0

1

0

0

1

1

1

0

0

Работа D- триггера

0

0

0

1

0

1

1

1

1

1

0

1

1

0

Работа D- триггера

0

0

0

1

0

0

1

1

1

0

0

0

0

1

Работа D- триггера

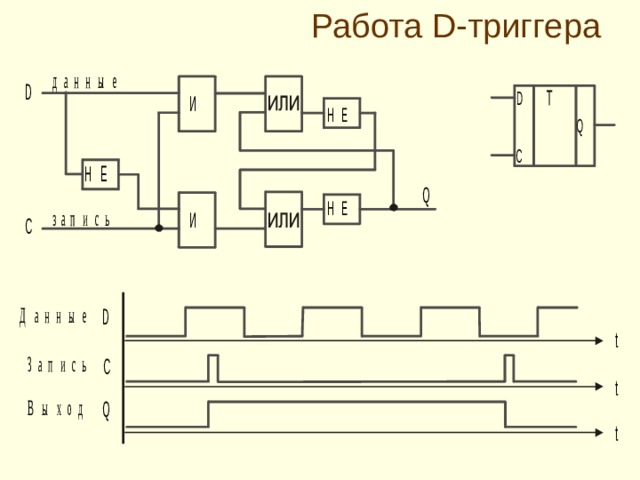

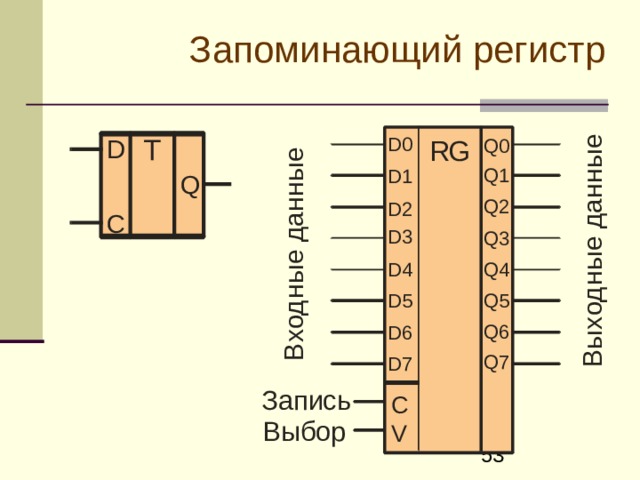

Запоминающий регистр

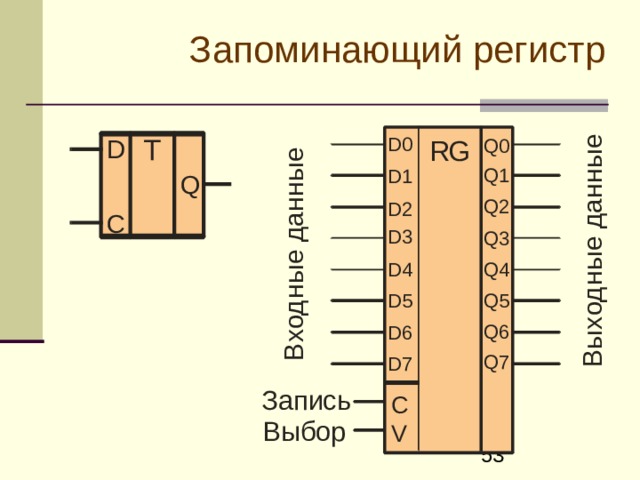

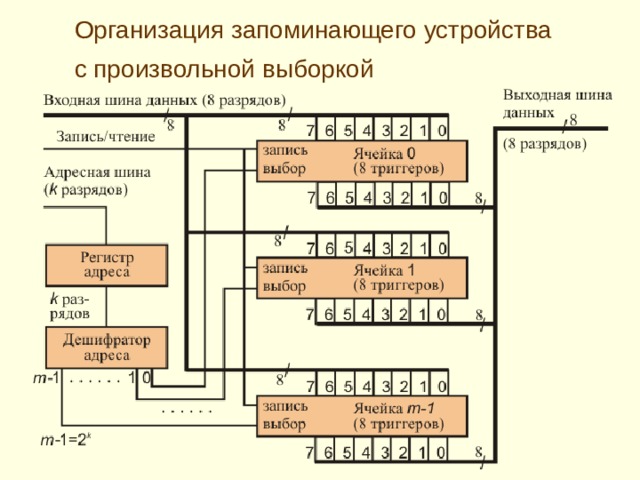

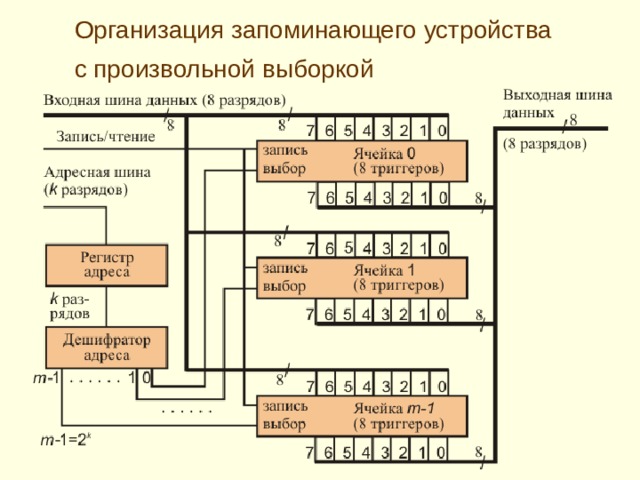

Организация запоминающего устройства с произвольной выборкой

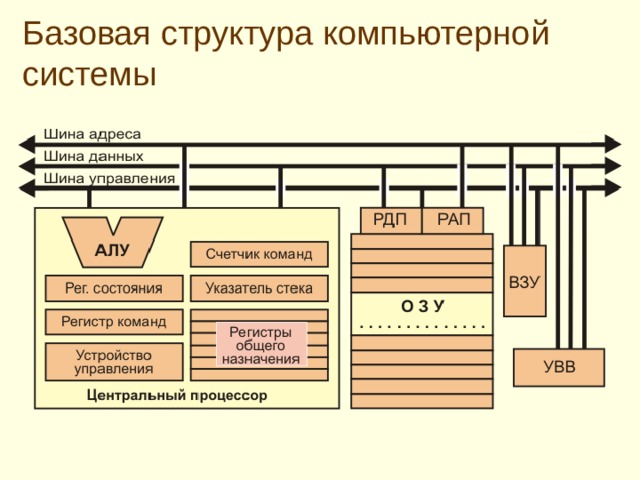

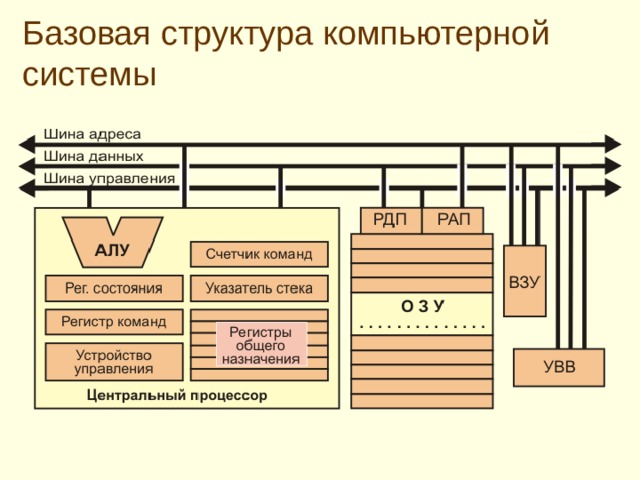

Базовая структура компьютерной системы

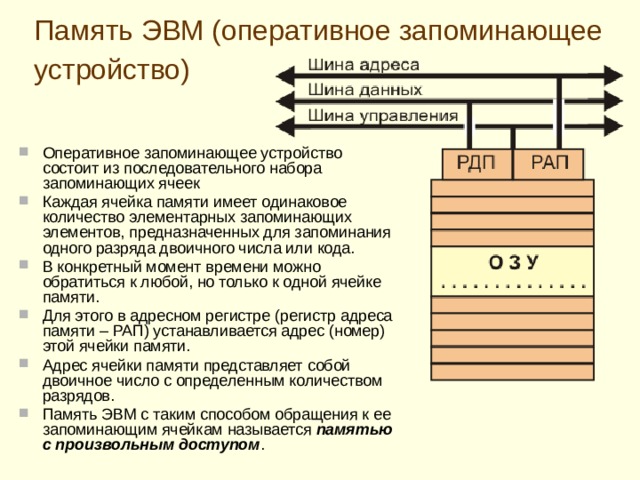

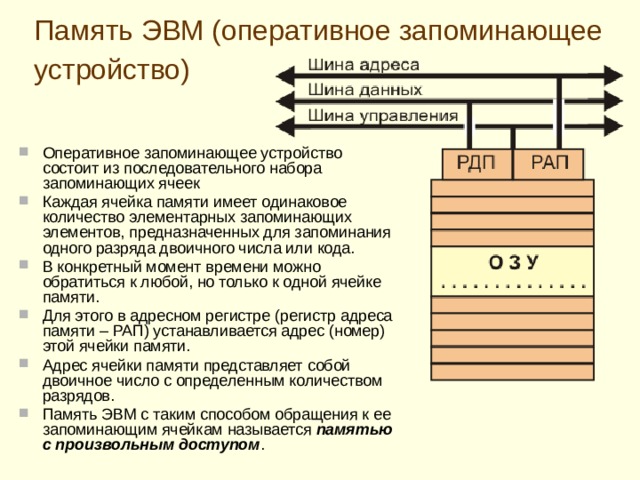

Память ЭВМ (оперативное запоминающее устройство)

- О перативное запоминающее устройство состоит из последовательного набора запоминающих ячеек

- Каждая ячейка памяти имеет одинаковое количество элементарных запоминающих элементов, предназначенных для запоминания одного разряда двоичного числа или кода.

- В конкретный момент времени можно обратиться к любой, но только к одной ячейке памяти.

- Для этого в адресном регистре (регистр адреса памяти – РАП) устанавливается адрес (номер) этой ячейки памяти.

- Адрес ячейки памяти представляет собой двоичное число с определенным количеством разрядов.

- Память ЭВМ с таким способом обращения к ее запоминающим ячейкам называется памятью с произвольным доступом .

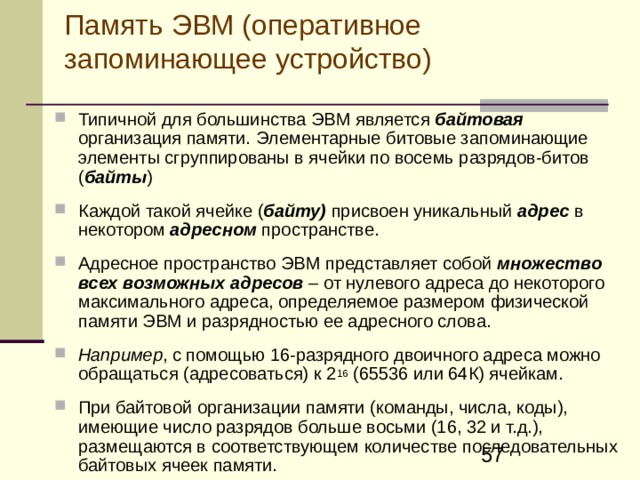

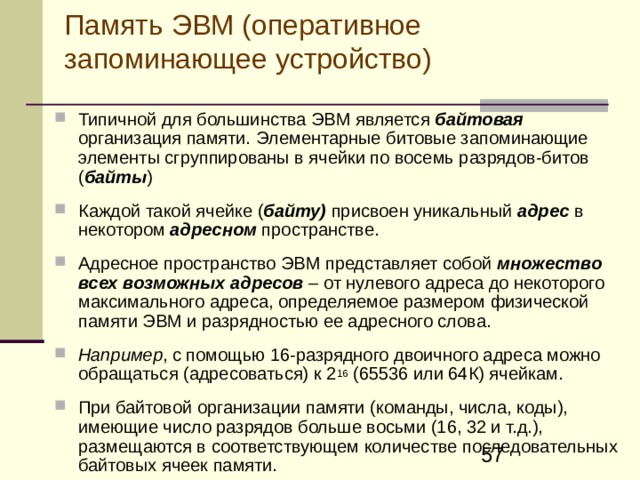

Память ЭВМ (оперативное запоминающее устройство)

- Типичной для большинства ЭВМ является байтовая организация памяти. Э лементарные битовые запоминающие элементы сгруппированы в ячейки по восемь разрядов-битов ( байт ы )

- К аждой такой ячейке ( байту) присвоен уникальный адрес в некотором адресном пространстве.

- Адресное пространство ЭВМ представляет собой множеств о всех возможных адресов – от нулевого адреса до некоторого максимального адреса, определяемое размером физической памяти ЭВМ и разрядностью ее адресного слова.

- Например , с помощью 16-разрядного двоичного адреса можно обращаться (адресоваться) к 2 16 (65536 или 64К) ячейкам.

- При байтовой организации памяти (команды, числа, коды), имеющие число разрядов больше восьми (16, 32 и т.д.), размещаются в соответствующем количестве последовательных байтовых ячеек памяти.

Память ЭВМ

Другие способы организации памяти :

- С тек . Выборка информации осуществляется не по адресу, а через «вершину» стека

- А ссоциативн ая память. Выборка информации из осуществляться не по месту расположения информации в памяти (адресу), а ассоциативно по содержанию хранящейся информации

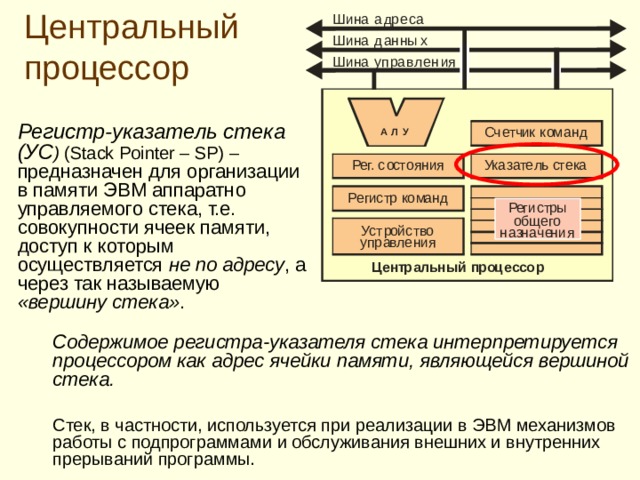

Центральный процессор

- Процессор компьютера – это устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом .

- Процессор дешифрует и выполняет команды программы,

- О рганизует обращения к оперативной памяти,

- И нициирует работу периферийных устройств, воспринимает и обрабатывает запросы, поступающие из устройств компьютера и из внешней среды («запросы прерывания»)

Важнейшими характеристиками процессора являются:

Количество разрядов чисел, над которыми он может совершать операции (например, 16‑разрядные процессоры PDP -11, Intel 80286, 32-разрядные VAX -11, Intel 80386 и 80486, Pentium , 64‑разрядные процессоры Alpha , Pentium IV

Набор команд, которые данный процессор может выполнять

Обычно характеризуют количеством команд, выполняемых процессором в секунду. Косвенным показателем быстродействия процессора является его тактовая частота: чем выше частота, тем больше быстродействие.

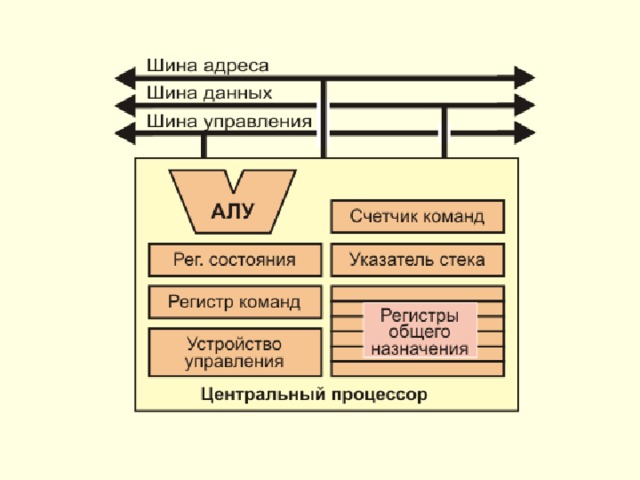

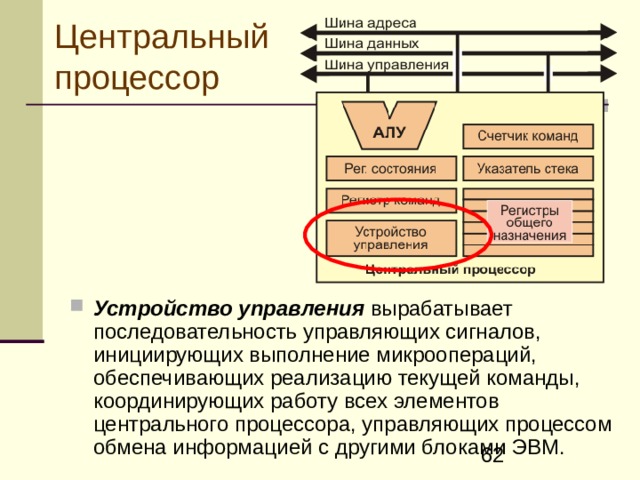

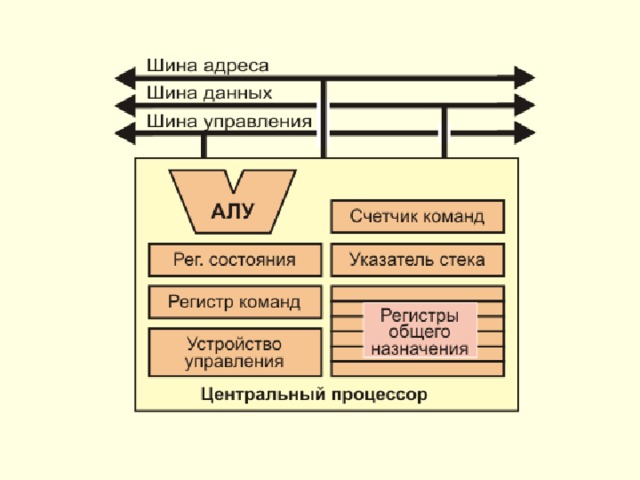

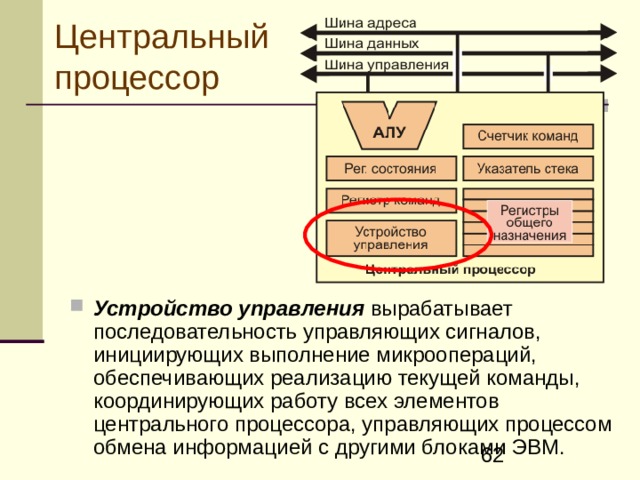

Центральный процессор

- Устройство управления вырабатывает последовательность управляющих сигналов, инициирующих выполнение микроопераций, обеспечивающих реализацию текущей команды, координирующих работу всех элементов центрального процессора, управляющих процессом обмена информацией с другими блоками ЭВМ.

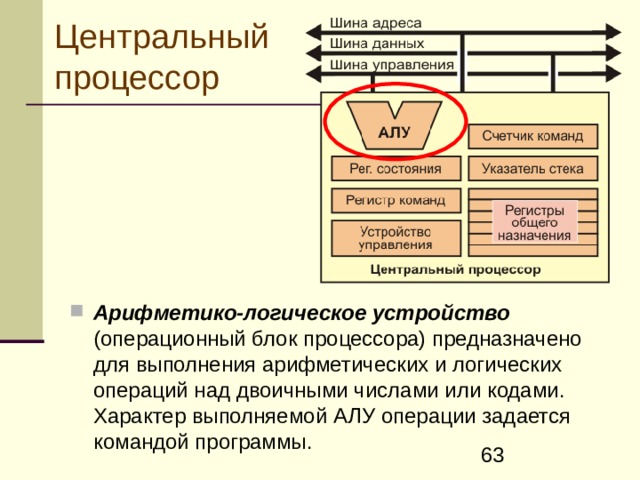

Центральный процессор

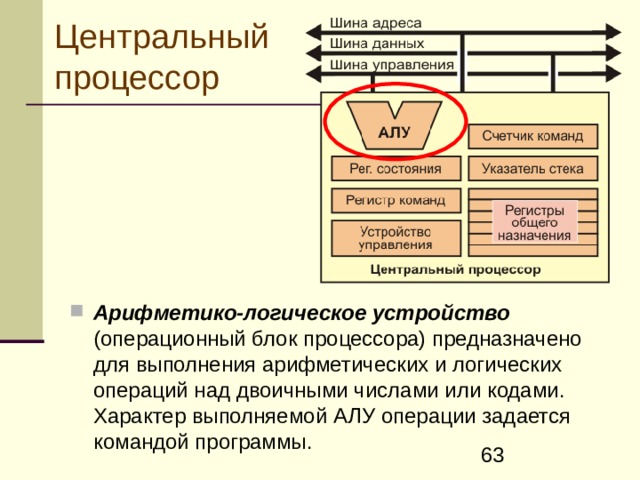

- Арифметико-логическое устройство (операционный блок процессора) предназначено для выполнения арифметических и логических операций над двоичными числами или кодами. Характер выполняемой АЛУ операции задается командой программы.

Центральный процессор

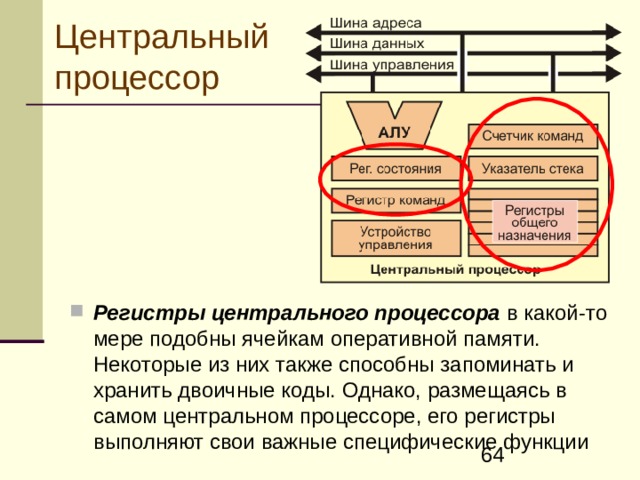

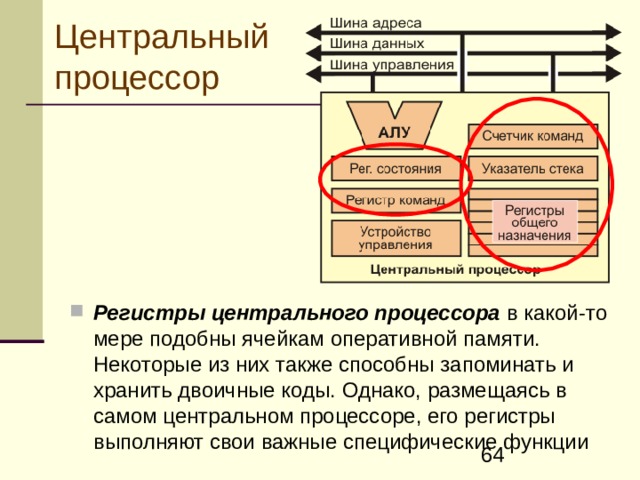

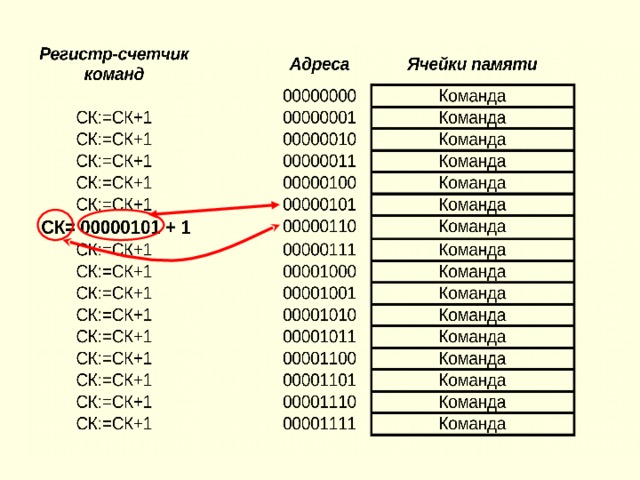

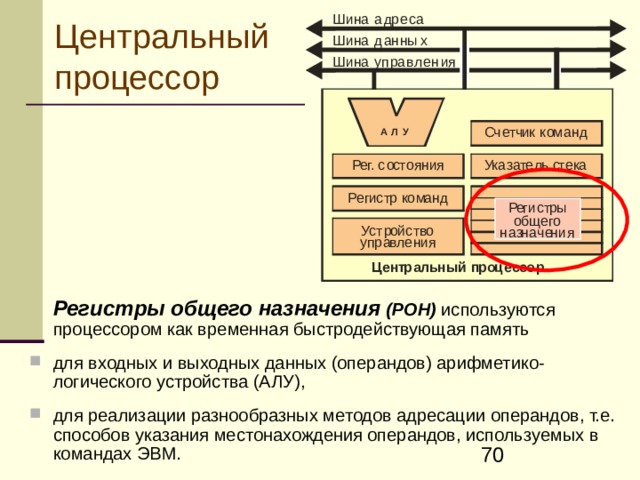

- Регистры центрального процессора в какой-то мере подобны ячейкам оперативной памяти. Некоторые из них также способны запоминать и хранить двоичные коды. Однако, размещаясь в самом центральном процессоре, его регистры выполняют свои важные специфические функции

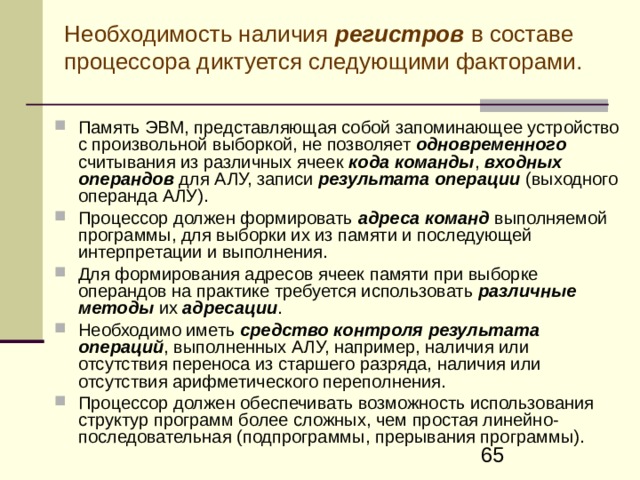

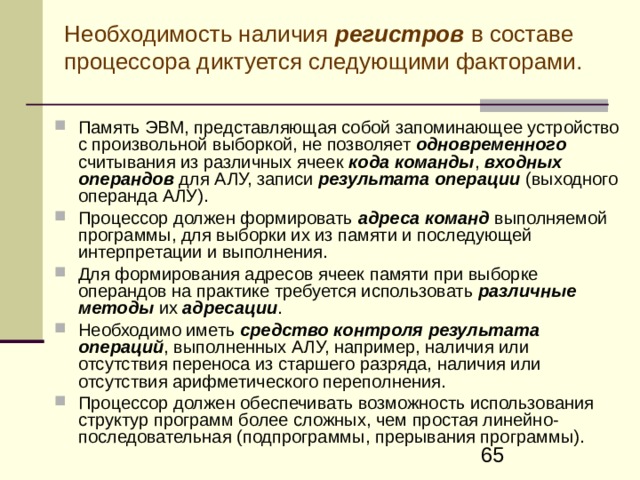

Необходимость наличия регистров в составе процессора диктуется следующими факторами.

- Память ЭВМ, представляющая собой запоминающее устройство с произвольной выборкой, не позволяет одновременного считывания из различных ячеек кода команды , входных операндов для АЛУ, записи результата операции (выходного операнда АЛУ).

- Процессор должен формировать адреса команд выполняемой программы, для выборки их из памяти и последующей интерпретации и выполнения.

- Для формирования адресов ячеек памяти при выборке операндов на практике требуется использовать различные методы их адресации .

- Необходимо иметь средство контроля результата операций , выполненных АЛУ, например, наличия или отсутствия переноса из старшего разряда, наличия или отсутствия арифметического переполнения.

- Процессор должен обеспечивать возможность использования структур программ более сложных, чем простая линейн о-последовательная ( подпрограмм ы , прерывания программ ы) .

Центральный процессор

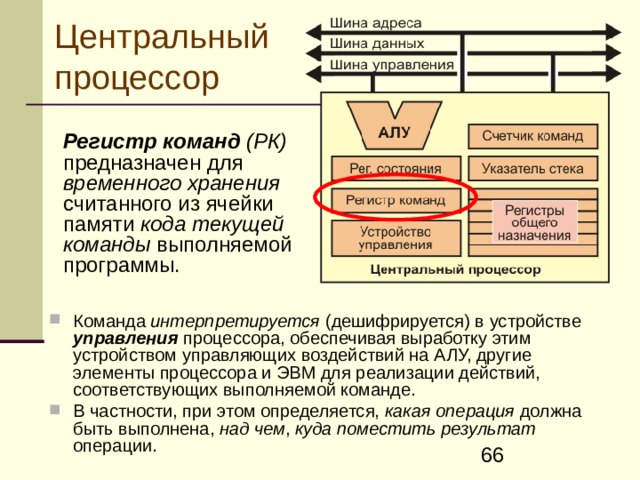

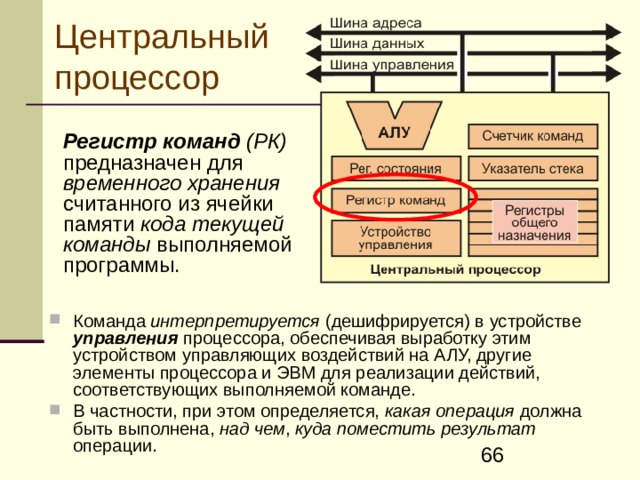

Регистр команд (РК) предназначен для временного хранения считанного из ячейки памяти кода текущей команды выполняемой программы.

- К оманда интерпретируется ( дешифрируется ) в устройстве управления процессора, обеспечивая выработку этим устройством управляющих воздействий на АЛУ, другие элементы процессора и ЭВМ для реализации действий, соответствующих выполняемой команде.

- В частности, при этом определяется, какая операция должна быть выполнена, над чем , куда поместить результат операции.

Центральный процессор

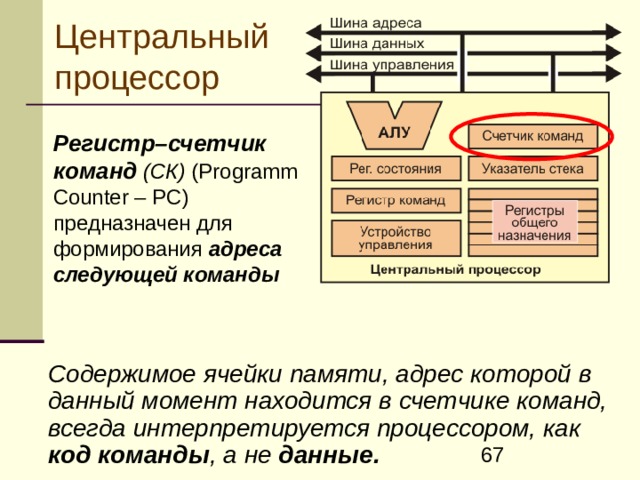

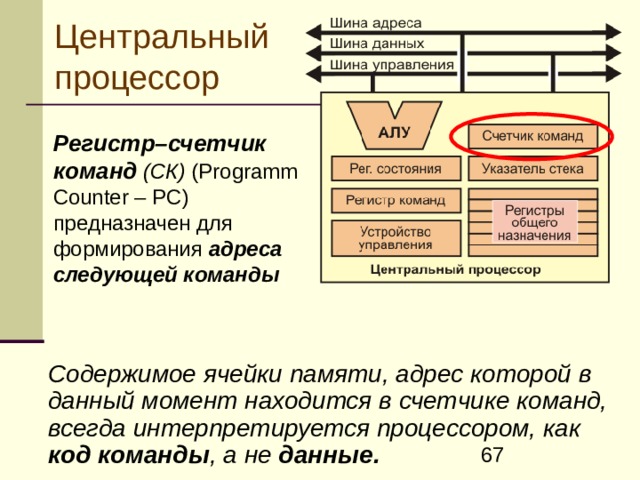

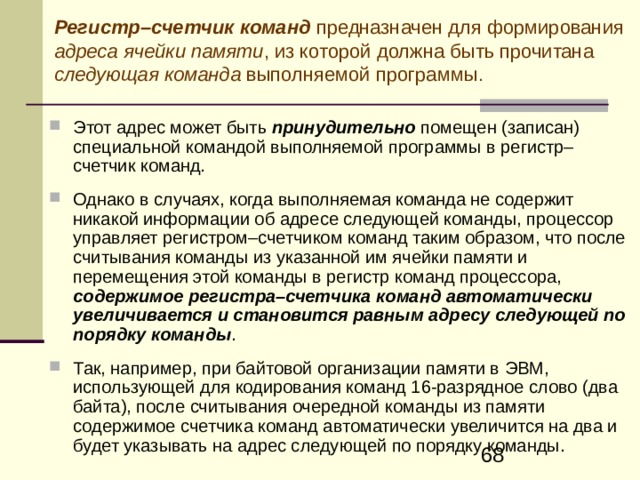

Регистр–счетчик команд (СК) (Programm Counter – PC) предназначен для формирования адреса следующей команды

С одержимое ячейки памяти, адрес которой в данный момент находится в счетчике команд, всегда интерпретируется процессором, как код команды , а не данные.

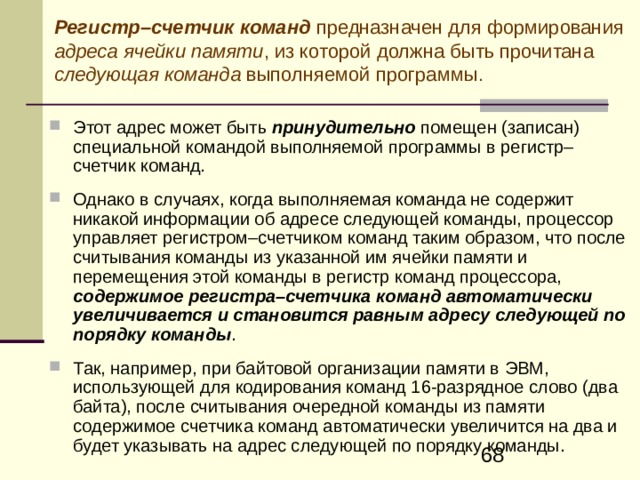

Регистр–счетчик команд предназначен для формирования адреса ячейки памяти , из которой должна быть прочитана следующая команда выполняемой программы.

- Этот адрес может быть принудительно помещен (записан) специальной командой выполняемой программы в регистр–счетчик команд.

- Однако в случаях, когда выполняемая команда не содержит никакой информации об адресе следующей команды, процессор управляет регистром–счетчиком команд таким образом, что после считывания команды из указанной им ячейки памяти и перемещения этой команды в регистр команд процессора, содержимое регистра–счетчика команд автоматически увеличивается и становится равным адресу следующей по порядку команды .

- Так, например, при байтовой организации памяти в ЭВМ, использующей для кодирования команд 16-разрядное слово (два байта), после считывания очередной команды из памяти содержимое счетчика команд автоматически увеличится на два и будет указывать на адрес следующей по порядку команды.

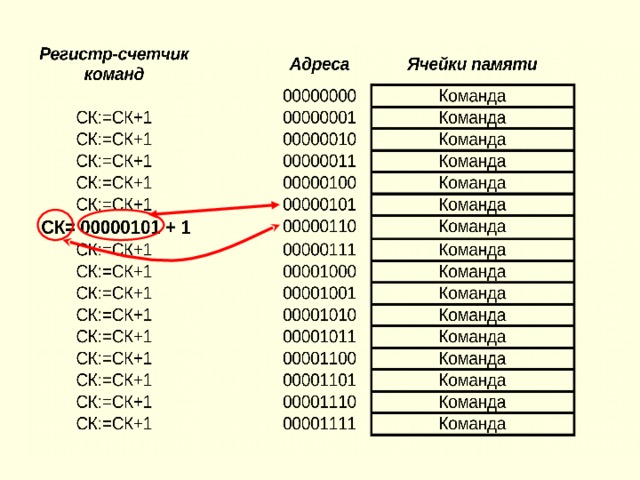

СК= 00000101 + 1

Центральный процессор

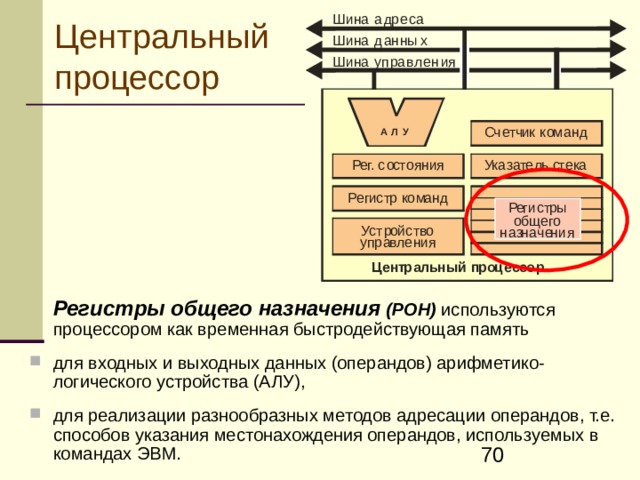

Регистры общего назначения (РОН) используются процессором как временная быстродействующая память

- для входных и выходных данных (операндов) арифметико-логического устройства (АЛУ),

- для реализации разнообразных методов адресации операндов, т.е. способов указания местонахождения операндов, используемых в командах ЭВМ.

Центральный процессор

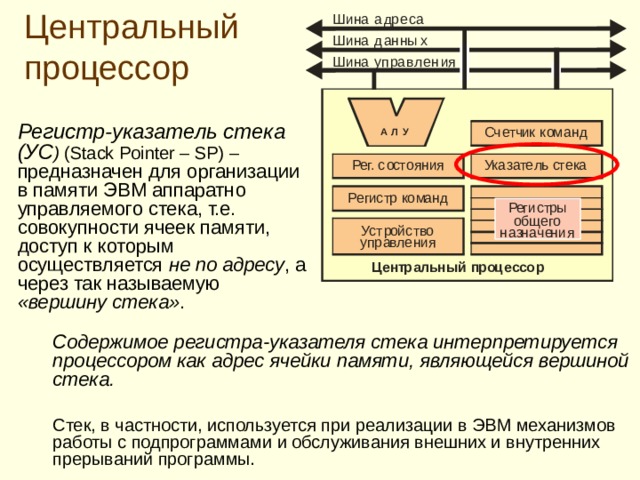

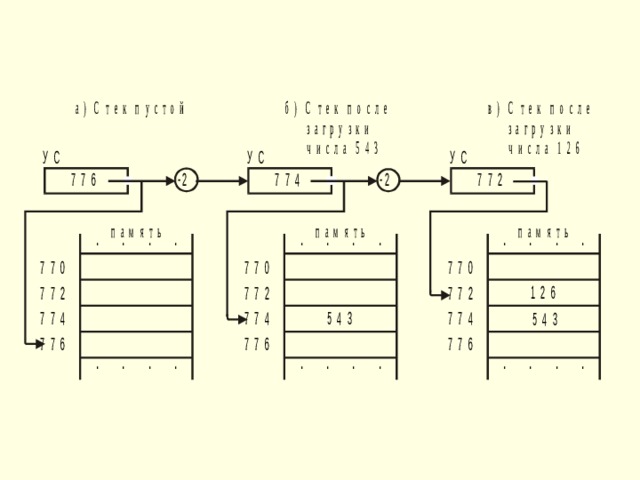

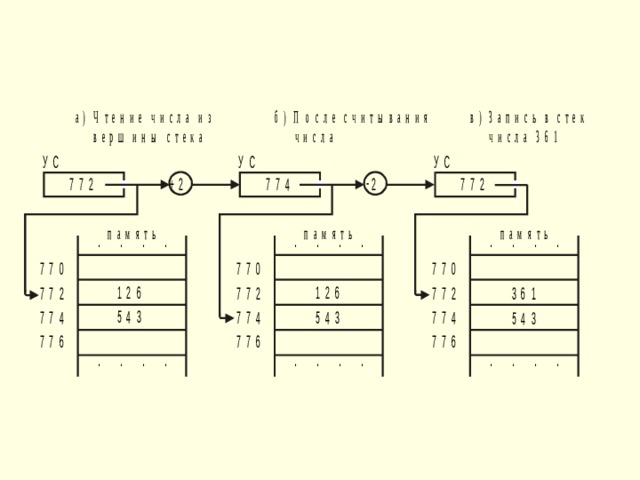

Регистр-указатель стека (УС ) (Stack Pointer – SP) – предназначен для организации в памяти ЭВМ аппаратно управляемого стека, т.е. совокупности ячеек памяти, доступ к которым осуществляется не по адресу , а через так называемую «вершину стека» .

Содержимое регистра-указателя стека интерпретируется процессором как адрес ячейки памяти, являющейся вершиной стека.

Стек, в частности, используется при реализации в ЭВМ механизмов работы с подпрограммами и обслуживания внешних и внутренних прерываний программы.

Центральный процессор

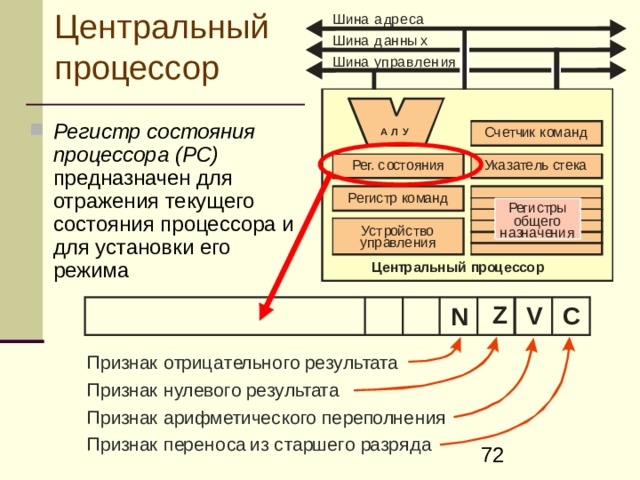

- Регистр состояния процессора (РС) предназначен для отражения текущего состояния процессора и для установки его режима

Центральный процессор

Регистр-

указатель стека (УС) (Stack Pointer – SP)

- Р егистр процессора, предназначенный для организации в памяти ЭВМ аппаратно управляемого стека ,

т.е. совокупности ячеек памяти, доступ к которым осуществляется не по адресу , а через так называемую « вершину стека » .

Содержимое регистра-указателя стека интерпретируется процессором как адрес ячейки памяти, являющейся вершиной стека.

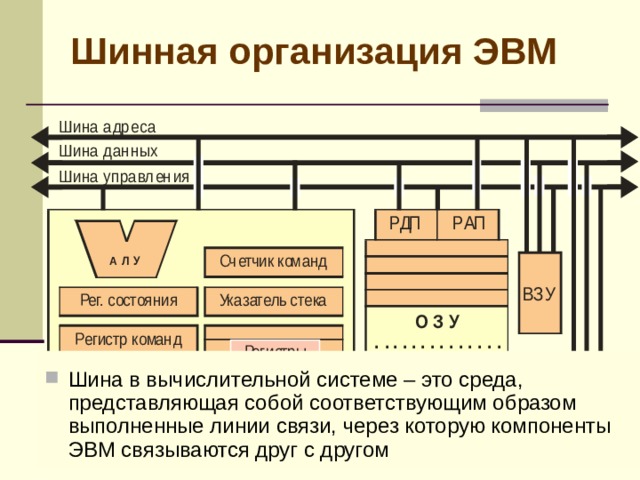

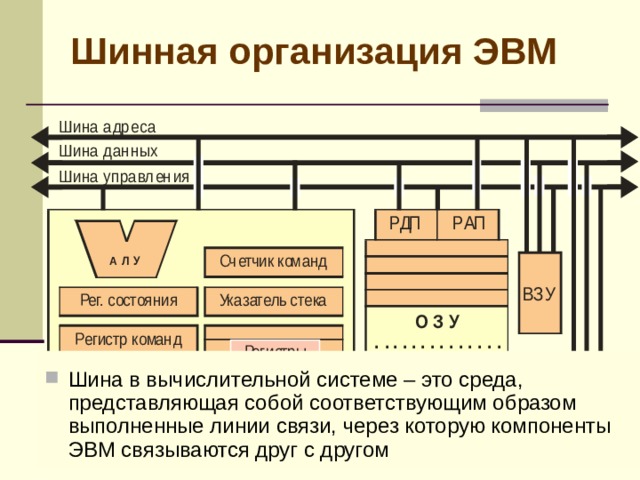

Шинная организация ЭВМ

- Шина в вычислительной системе – это среда, представляющая собой соответствующим образом выполненные линии связи, через которую компоненты ЭВМ связываются друг с другом

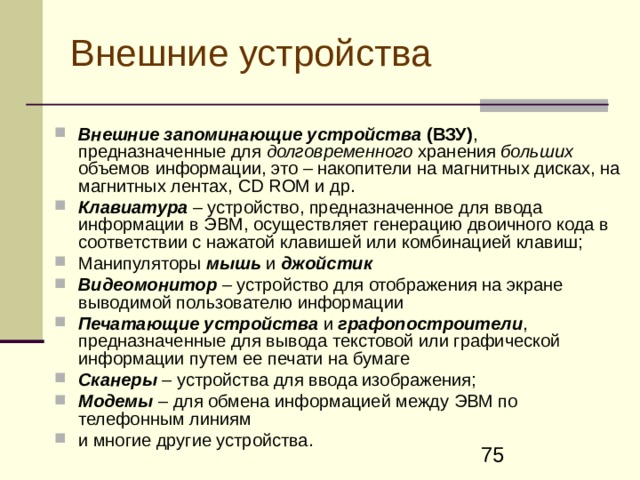

Внешние устройства

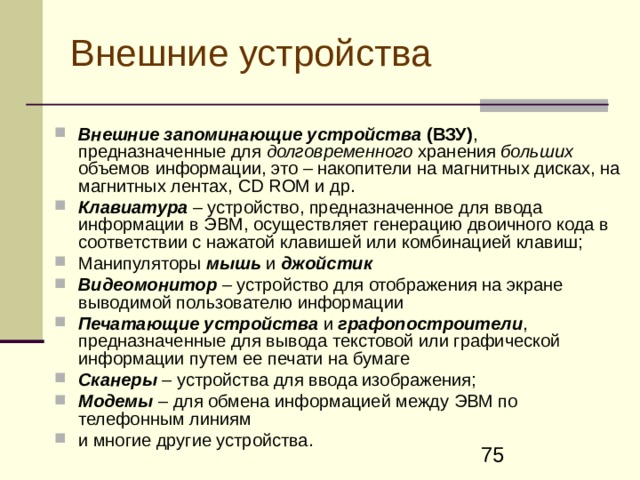

- Внешние запоминающие устройства (ВЗУ) , предназначенные для долговременного хранения больших объемов информации, это – накопители на магнитных дисках, на магнитных лентах, CD ROM и др.

- Клавиатура – устройство, предназначенное для ввода информации в ЭВМ, осуществляет генерацию двоичного кода в соответствии с нажатой клавишей или комбинацией клавиш;

- Манипуляторы мышь и джойстик

- Видеомонитор – устройство для отображения на экране выводимой пользователю информации

- Печатающие устройства и графопостроители , предназначенные для вывода текстовой или графической информации путем ее печати на бумаге

- Сканеры – устройства для ввода изображения;

- Модемы – для обмена информацией между ЭВМ по телефонным линиям

- и многие другие устройства.

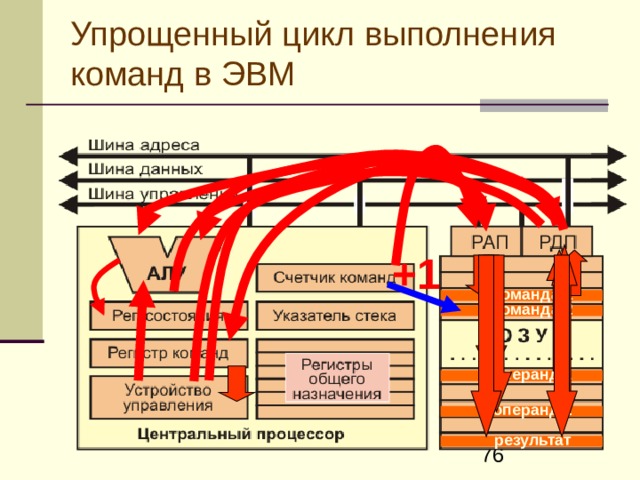

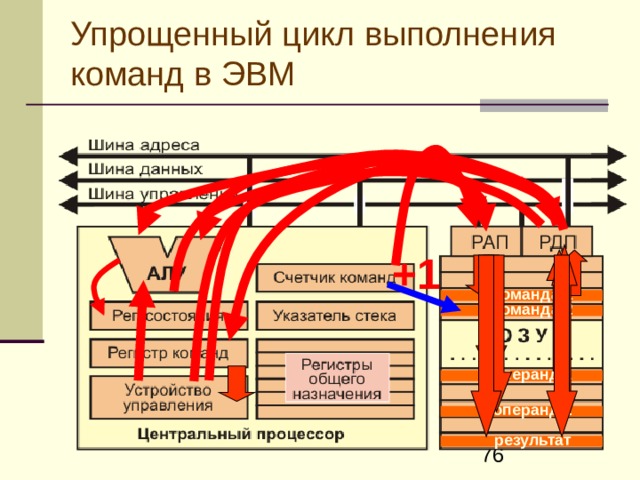

Упрощенный цикл выполнения команд в ЭВМ

+1

команда 1

команда 2

операнд 1

операнд 2

результат

Упрощенный цикл выполнения команд

- Процессор помещает содержимое своего регистра-счетчика команд в регистр адреса памяти (РАП) запоминающего устройства.

- Затем из ячейки памяти, адрес которой помещен в РАП, извлекается код команды и через регистр данных памяти (РДП) и шину данных передается в регистр команд процессора.

- После считывания из памяти содержимого ячейки, адрес которой указывается регистром–счетчиком команд, содержимое этого регистра автоматически увеличивается и становится равным адресу следующего по порядку слова. (Например, если команды занимают в памяти ЭВМ два байта, то увеличение счетчика команд производится на два).

- Вслед за этим устройство управления процессора начинает интерпретацию команды, находящейся в его регистре команд.

- Вначале определяется операция, которая должна быть выполнена процессором по данной команде, и в соответствии с ней вырабатываются сигналы для управления элементами процессора, в частности, сигналы, осуществляющие переключение АЛУ в режим выполнения нужной операции.

Предположим, что, выполняется команда сложения двух чисел, находящихся в ячейках памяти

- Декодируя код операции, задаваемый командой, устройство управления процессора определяет, необходимость выборки операндов для выполнения конкретной команды.

(В рассматриваемом примере необходимы два операнда).

- Устройство управления в результате дальнейшей интерпретации команды определяет адрес первого операнда и помещает его в РАП.

- Содержимое этой ячейки, т.е. первый операнд, считывается и через РДП по шине данных передается в один из регистров процессора, подключенного к входу первого операнда АЛУ.

- Затем определяется адрес второго операнда, производится его считывание в регистр и установка на другом входе АЛУ.

- После выборки и подготовки необходимых команде операндов соответствующая ей операция выполняется (в данном примере происходит сложение выбранных операндов).

- Состояние результата операции отражается в регистре состояния процессора

- Результат операции пересылается в память ЭВМ по адресу, также определяемому устройством управления в результате интерпретации кода команды

- Процессор готов к выборке следующей команды (ее адрес находится в его регистре-счетчике команд)

Система команд ЭВМ и адресация операндов

- Команда представляет собой код, определяющий операцию вычислительной машины и данные, участвующие в операции.

- Команда содержит в явной или неявной форме информацию об адресе, по которому размещается результат операции, и об адресе следующей команды.

- Под системой команд ЭВМ обычно понимают набор инструкций, которые может выполнять ее центральный процессор, способы кодирования этих инструкций и методы указания местонахождения операндов.

Типы команд

- По характеру выполняемых операций различают следующие основные группы команд:

- команды арифметических операций, команды логических (поразрядных) операций (И, ИЛИ, НЕ и др.),

- команды пересылки кодов между компонентами ЭВМ,

- команды управления порядком выборки и исполнения команд (команды передачи управления),

- команды задания режима работы процессора и др.

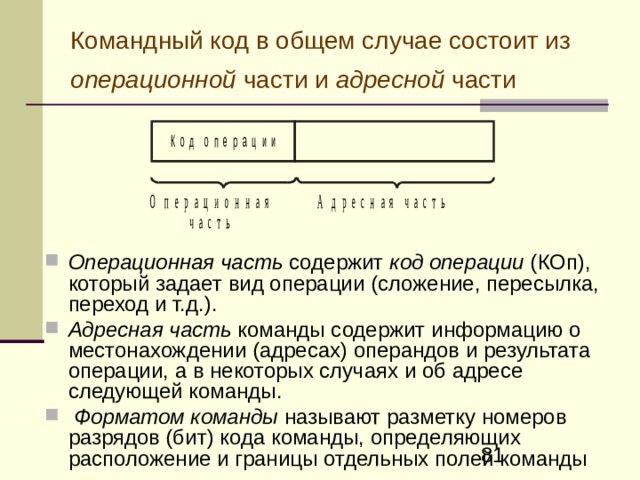

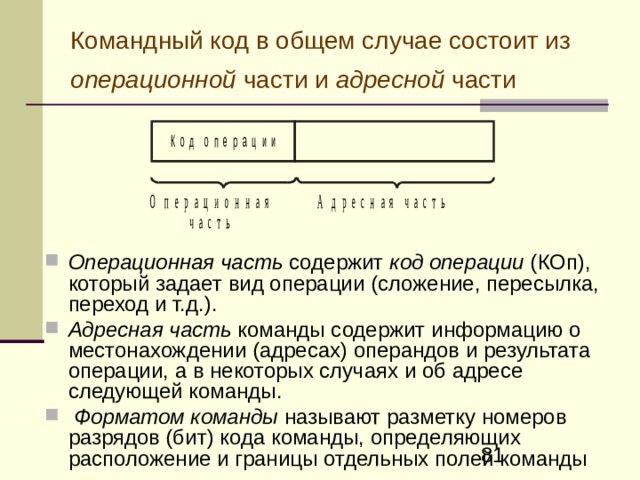

К омандный код в общем случае состоит из операционной части и адресной части

- Операционная часть содержит код операции (КОп), который задает вид операции (сложение, пересылка, переход и т.д.).

- Адресная часть команды содержит информацию о местонахождении (адресах) операндов и результата операции, а в некоторых случаях и об адресе следующей команды.

- Форматом команды называют разметку номеров разрядов (бит) кода команды, определяющих расположение и границы отдельных полей команды

В зависимости от количества операндов, можно представить следующие разновидности команд:

- одноадресные команды , оперирующие только одним операндом (например, команды ОЧИСТИТЬ ЯЧЕЙКУ ПАМЯТИ, УВЕЛИЧИТЬ ЗНАЧЕНИЕ ЯЧЕЙКИ НА ЕДИНИЦУ, ИЗМЕНЕНИТЬ ЗНАК ЧИСЛА и другие;

- двухадресные команды , для работы которых необходимо указание двух адресов (например, команда КОПИРОВАТЬ СОДЕРЖИМОЕ ОДНОЙ ЯЧЕЙ-КИ В ДРУГУЮ);

- трехадресные команды , например команда – СЛОЖИТЬ СОДЕРЖИ-МОЕ ДВУХ ЯЧЕЕК И РЕЗУЛЬТАТ ПОМЕСТИТЬ ПО ТРЕТЬЕМУ АДРЕСУ;

- четырехадресные , см. пример команды приведенной выше, но в которой добавлено указание адреса команды, которая должна выполняться после данной.

Способы адресации операндов

- Подразумеваемый операнд . В команде не содержится явных указаний об адресе операнда; операнд подразумевается и фактически задается кодом операции команды. Например, в команде УВЕЛИЧИТЬ ЧИСЛО НА ЕДИНИЦУ первый операнд

- Подразумеваемый адрес . В команде не содержится явных указаний об адресе участвующего в операции операнда или адреса, по которому помещается результат операции, но этот адрес подразумевается.

- Непосредственная адресация . В команде содержится не адрес операнда, а непосредственно сам операнд .

- Относительная адресация или базирование . Исполнительный адрес определяется суммой адресного кода и некоторого числа, называемого базовым адресом . Адресный код в этом случае играет роль смещения фактического исполнительного адреса относительно базового адреса.

- Регистровая адресация . При адресации операнда используется содержимое указанного в команде какого-либо регистра процессора.

- Косвенная адресация . Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Другими словами, косвенная адресация может быть определена как «адресация адреса». В некоторых ЭВМ используется многоступенчатая косвенная адресация.

Режимы адресации с помощью регистров общего назначения

- Регистровый метод адресации.

При использовании этого метода адресации в команде указывается регистр общего назначения (например, его номер) и содержимое этого регистра интерпретируется процессором как операнд.

- Косвенно-регистровый метод адресации.

Содержимое указанного в команде регистра интерпретируется процессором как адрес ячейки памяти, в которой находится операнд

- Автоинкрементный метод адресации (адресация с автоувеличением) .

Содержимое указанного в команде регистра интерпретируется процессором как адрес ячейки памяти, в которой находится операнд (как в косвенно-регистровом методе), но после выборки операнда содержимое регистра увеличивается (инкрементируется) обычно на 1 или 2, таким образом, чтобы указывать на адрес следующей по порядку ячейки памяти.

- Косвенно-автоинкрементный метод адресации.

Содержимое указанного в команде регистра интерпретируется процессором как адрес ячейки памяти, в которой находится адрес операнда, и после выборки операнда содержимое регистра (адрес адреса) увеличивается (инкрементируется), таким образом, чтобы указывать на адрес следующей по порядку ячейки.

- Автодекременный метод адресации (адресация с автоуменьшением) .

При интерпретации команды содержимое указанного в команде регистра вначале уменьшается (инкрементируется) обычно на 1 или 2, после чего уменьшенное содержимое регистра интерпретируется процессором как адрес ячейки памяти, в которой находится операнд.

- Косвенно-автодекременный метод адресации.

При интерпретации команды содержимое указанного в команде регистра вначале уменьшается (инкрементируется), после чего уменьшенное содержимое регистра интерпретируется процессором как адрес ячейки памяти, в которой находится адрес операнда.

- Косвенная адресация со смещением (индексный метод адресации).

При использовании этого метода адресации инструкция (команда) занимает в памяти на одно слово (ячейку) больше. В дополнительном слове команды указывается так называемое смещение (индексное слово). Исполнительный адрес операнда определяется в этом случае как сумма содержимого указанного в команде регистра и смещения (индексного слова).

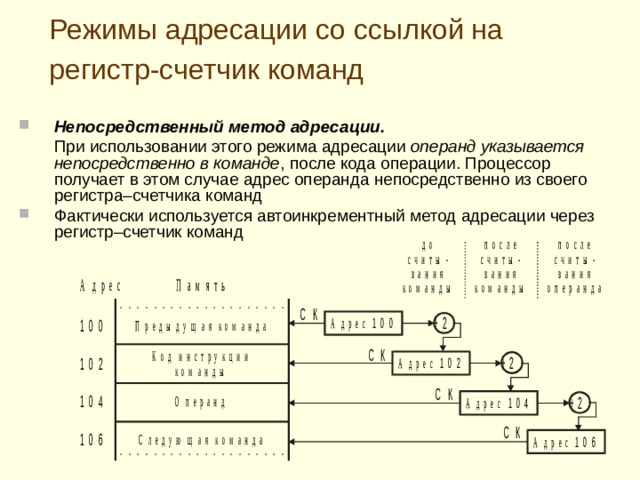

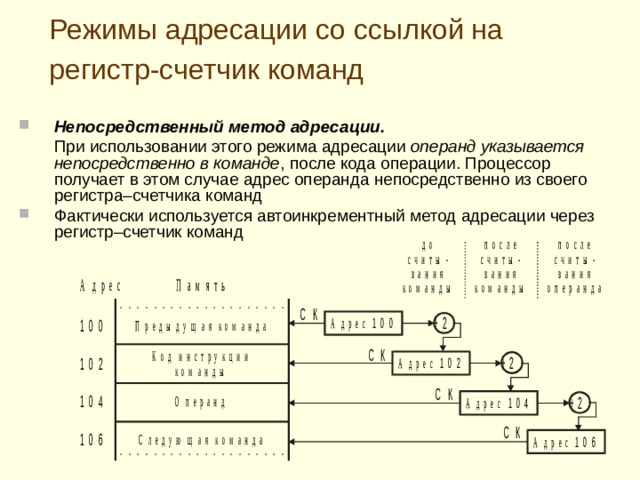

Режимы адресации со ссылкой на регистр-счетчик команд

- Непосредственный метод адресации.

При использовании этого режима адресации операнд указывается непосредственно в команде , после кода операции. Процессор получает в этом случае адрес операнда непосредственно из своего регистра–счетчика команд

- Ф актически используется автоинкрементный метод адресации через регистр–счетчик команд

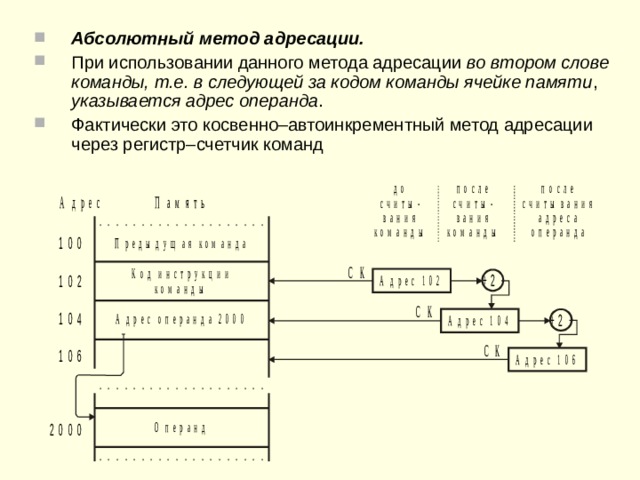

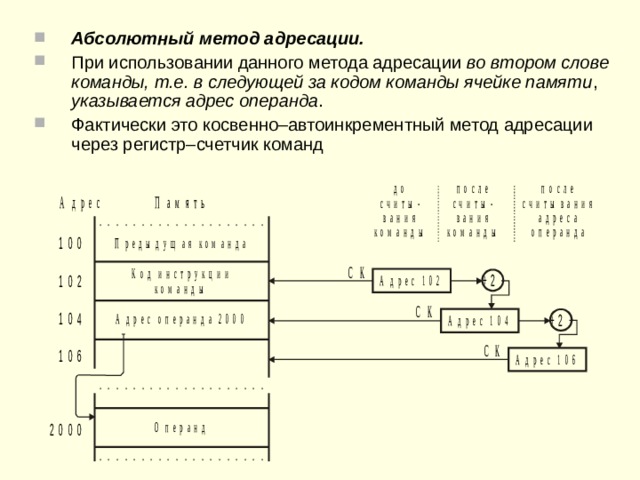

- Абсолютный метод адресации.

- При использовании данного метода адресации во втором слове команды, т.е. в следующей за кодом команды ячейке памяти , указывается адрес операнда .

- Фактически это косвенно–автоинкрементный метод адресации через регистр–счетчик команд

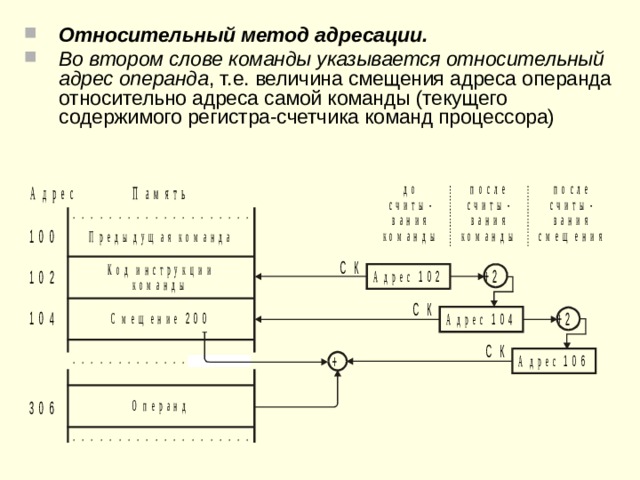

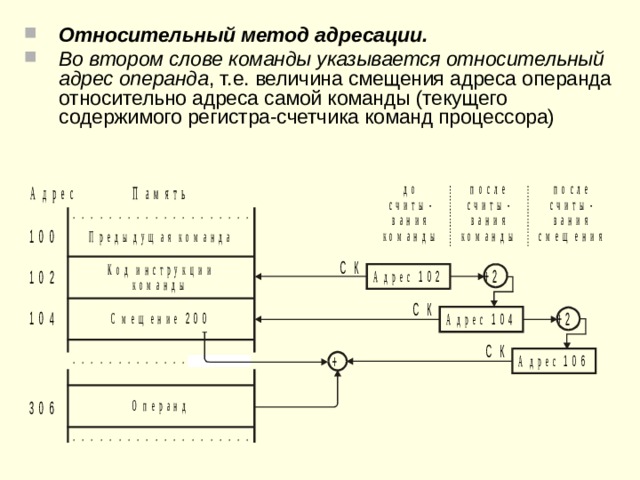

- Относительный метод адресации.

- Во втором слове команды указывается относительный адрес операнда , т.е. величина смещения адреса операнда относительно адреса самой команды (текущего содержимого регистра-счетчика команд процессора)

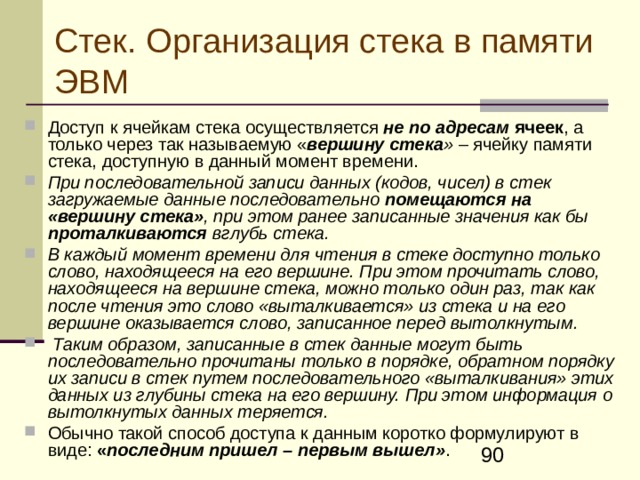

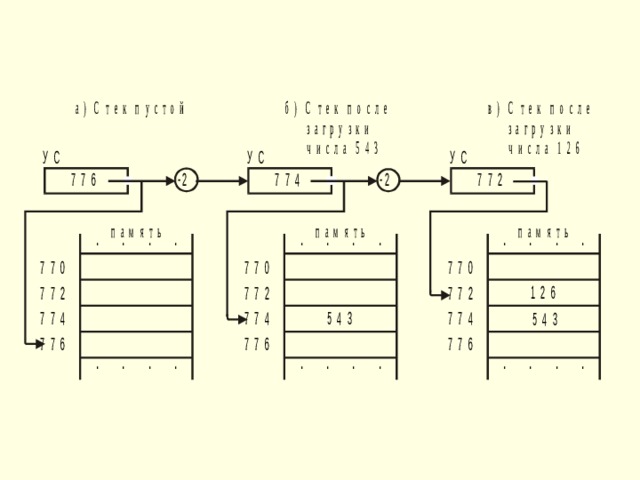

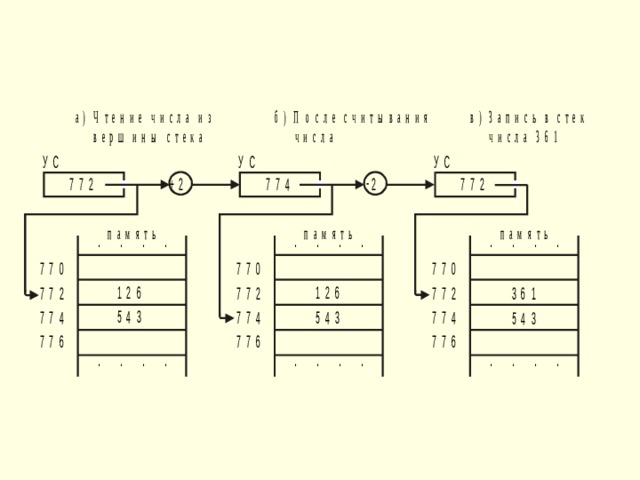

Стек. Организация стека в памяти ЭВМ

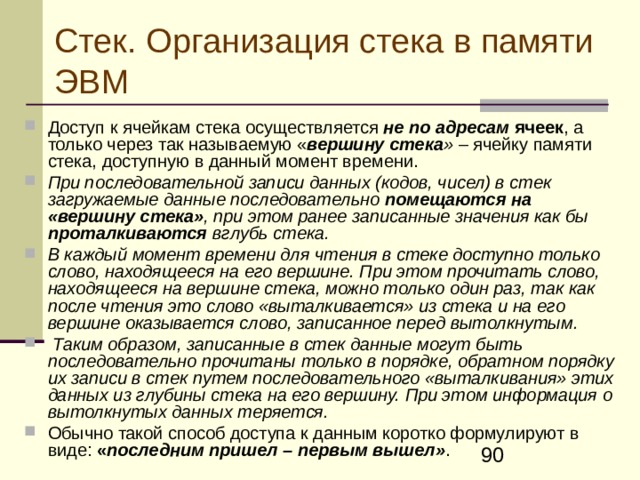

- Доступ к ячейкам стека осуществляется не по адресам ячеек , а только через так называемую « вершину стека » – ячейку памяти стека, доступную в данный момент времени.

- При последовательной записи данных (кодов, чисел) в стек загружаемые данные последовательно помещаются на «вершину стека» , при этом ранее записанные значения как бы проталкиваются вглубь стека.

- В каждый момент времени для чтения в стеке доступно только слово, находящееся на его вершине. При этом прочитать слово, находящееся на вершине стека, можно только один раз, так как после чтения это слово «выталкивается» из стека и на его вершине оказывается слово, записанное перед вытолкнутым.

- Таким образом, записанные в стек данные могут быть последовательно прочитаны только в порядке, обратном порядку их записи в стек путем последовательного «выталкивания» этих данных из глубины стека на его вершину. При этом информация о вытолкнутых данных теряется.

- Обычно такой способ доступа к данным коротко формулируют в виде: « последним пришел – первым вышел» .

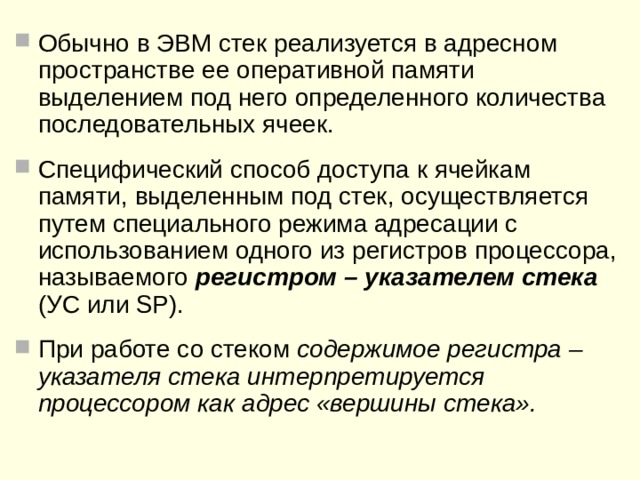

- Обычно в ЭВМ стек реализуется в адресном пространстве ее оперативной памяти выделением под него определенного количества последовательных ячеек.

- Специфический способ доступа к ячейкам памяти, выделенным под стек, осуществляется путем специального режима адресации с использованием одного из регистров процессора, называемого регистром – указателем стека (УС или SP).

- При работе со стеком содержимое регистра – указателя стека интерпретируется процессором как адрес «вершины стека».

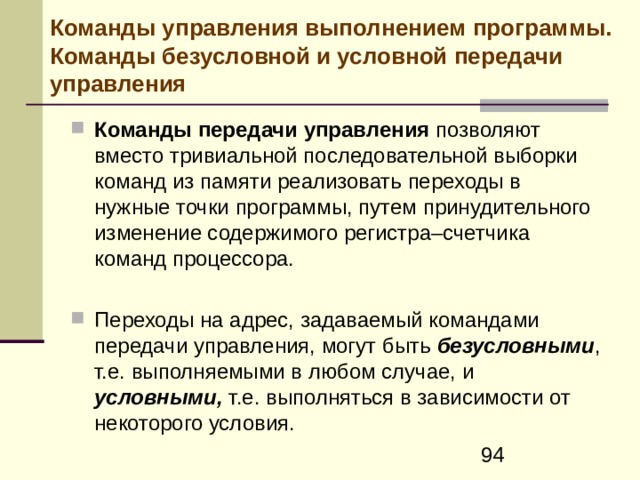

Команды управления выполнением программы. Команды безусловной и условной передачи управления

- К оманды передачи управления позволяют вместо тривиальной последовательной выборки команд из памяти реализовать переходы в нужные точки программы , путем принудительного изменение содержимого регистра–счетчика команд процессора.

- Переходы на адрес, задаваемый командами передачи управления, могут быть безусловными , т.е. выполняемыми в любом случае, и условными , т.е. выполняться в зависимости от некоторого условия .

- В системе команд ЭВМ существует целый набор разнообразных команд условных ветвлений .

- Это команды, осуществляющие переход в случае, например, когда результат предыдущей операции равен нулю , больше нуля , больше или равен нулю , меньше нуля и т.д.

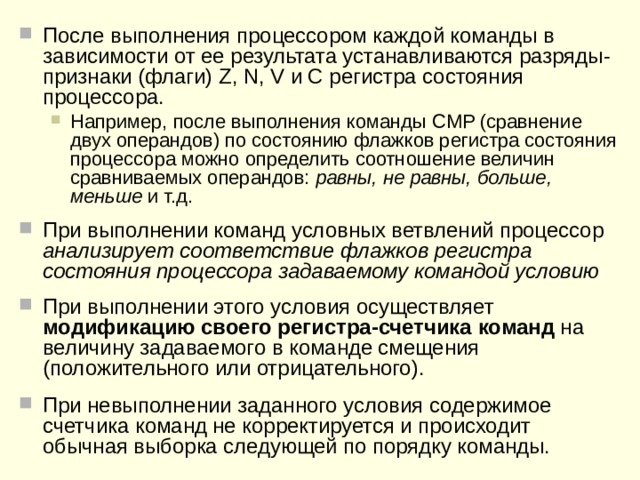

- П осле выполнения процессором каждой команды в зависимости от ее результата устанавливаются разряды - признаки (флаги) Z, N, V и C регистра состояния процессора.

- Например, после выполнения команды CMP (сравнение двух операндов) по состоянию флажков регистра состояния процессора можно определить соотношение величин сравниваемых операндов: равны, не равны, больше, меньше и т.д.

- Например, после выполнения команды CMP (сравнение двух операндов) по состоянию флажков регистра состояния процессора можно определить соотношение величин сравниваемых операндов: равны, не равны, больше, меньше и т.д.

- При выполнении команд условных ветвлений процессор анализирует соответствие флажков регистра состояния процессора задаваемому командой условию

- П ри выполнении этого условия осуществляет модификацию своего регистра-счетчика команд на величину задаваемого в команде смещения (положительного или отрицательного).

- При невыполнении заданного условия содержимое счетчика команд не корректируется и происходит обычная выборка следующей по порядку команды.

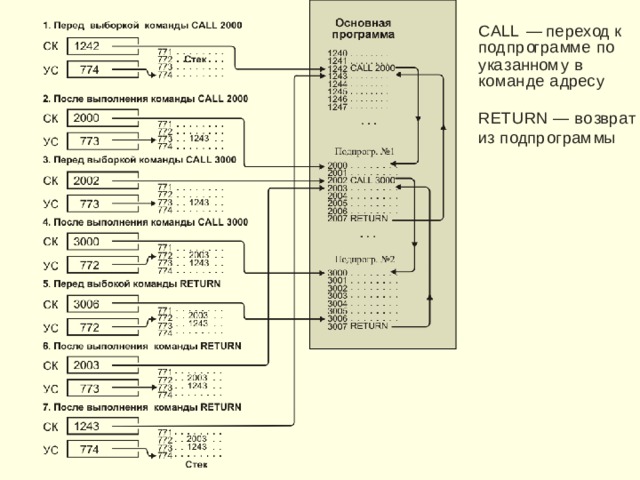

Подпрограммы .

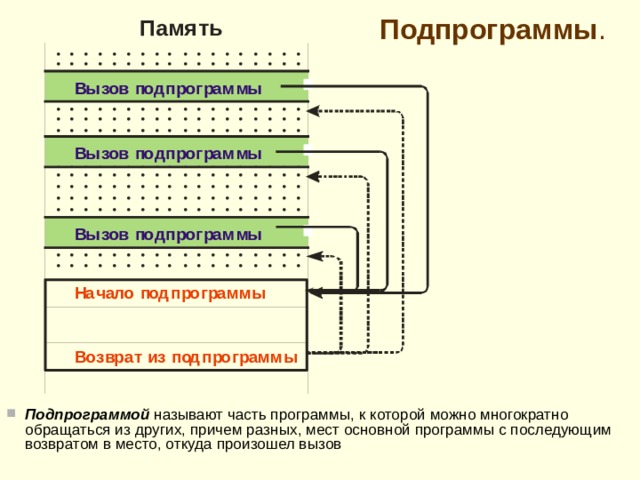

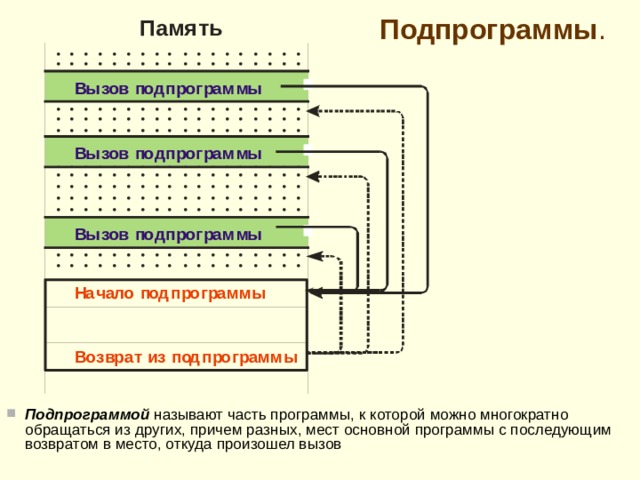

- Подпрограммой называют часть программы, к которой можно многократно обращаться из других, причем разных, мест основной программы с последующим возвратом в место, откуда произошел вызов

Подпрограммы

- П ри реализации механизма работы с подпрограммами существенными являются два момента:

- вызов подпрограммы , т.е. передача управления на адрес первой команды подпрограммы, и

- возврат из подпрограммы , т.е. переход к команде, адрес которой является следующим за командой вызвавшей подпрограмму

- Б олее сложной задачей является решение проблемы возврата из подпрограммы.

- Дело в том, что адрес возврата из подпрограммы заранее не известен и жестко связан с адресом команды вызова подпрограммы.

- Это делает невозможным указание этого адреса в команде, осуществляющей возврат из подпрограммы .

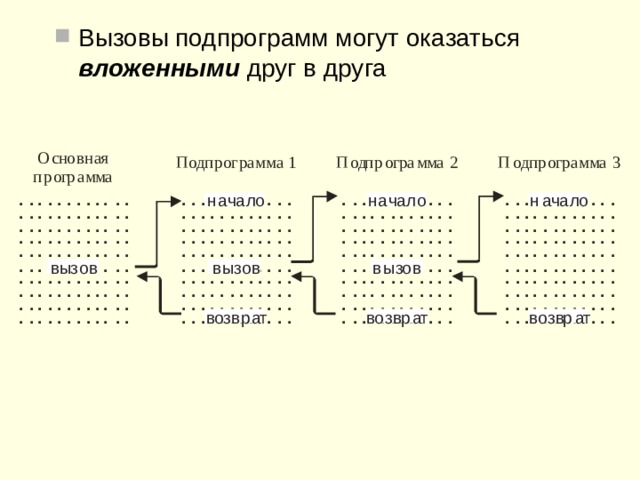

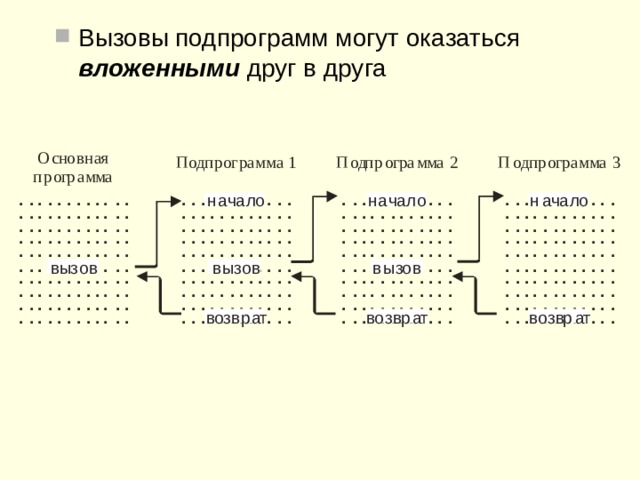

- В ызовы подпрограмм могут оказаться вложенными друг в друга

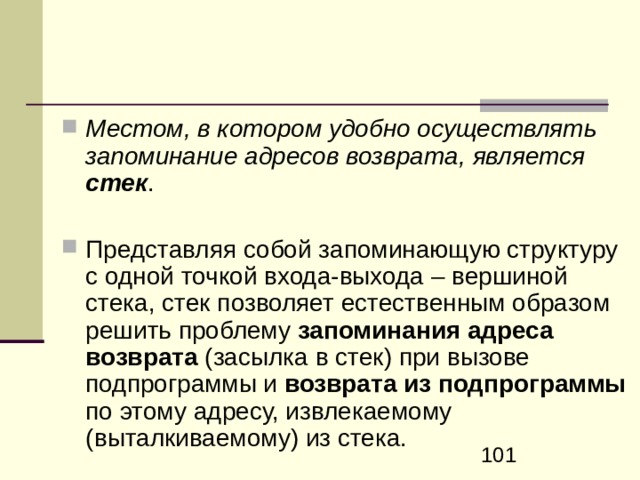

- Местом, в котором удобно осуществлять запоминание адресов возврата, является стек .

- Представляя собой запоминающую структуру с одной точкой входа-выхода – вершиной стека, стек позволяет естественным образом решить проблему запоминания адреса возврата (засылка в стек) при вызове подпрограммы и возврата из подпрограммы по этому адресу, извлекаемому (выталкиваемому) из стека.

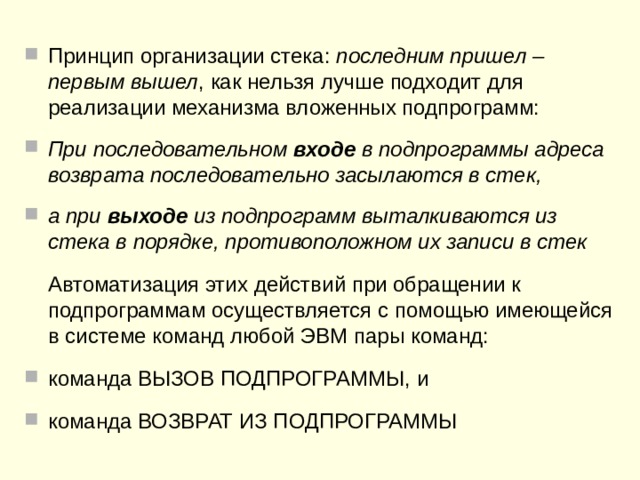

- Принцип организации стека: последним пришел – первым вышел , как нельзя лучше подходит для реализации механизма вложенных подпрограмм:

- П ри последовательном входе в подпрограммы адреса возврата последовательно засылаются в стек,

- а при выходе из подпрограмм выталкиваются из стека в порядке, противоположном их записи в стек

А втоматизация этих действий при обращении к подпрограммам осуществляется с помощью имеющейся в системе команд любой ЭВМ пары команд :

- команда ВЫЗОВ ПОДПРОГРАММЫ, и

- команда ВОЗВРАТ ИЗ ПОДПРОГРАММЫ

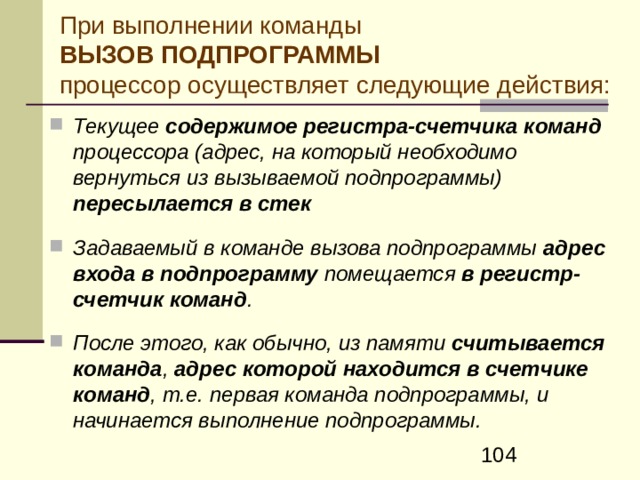

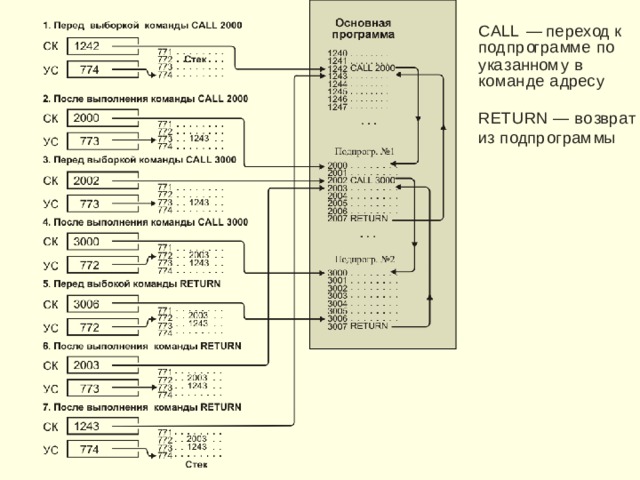

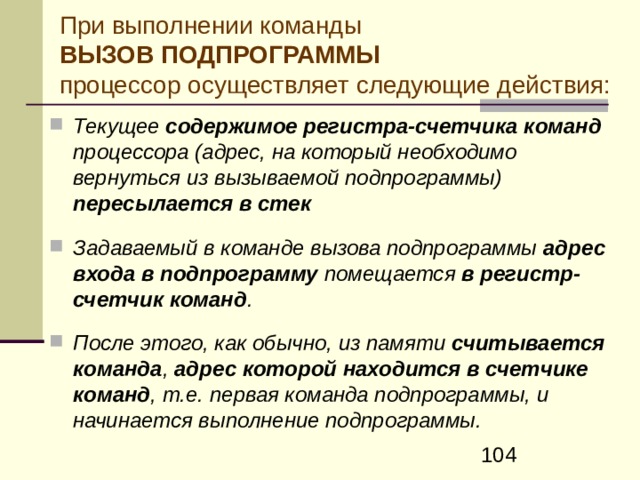

При выполнении команды ВЫЗОВ ПОДПРОГРАММЫ процессор осуществляет следующие действия:

- Текущее содержимое регистра-счетчика команд процессора (адрес, на который необходимо вернуться из вызываемой подпрограммы) пересылается в стек

- Задаваемый в команде вызова подпрограммы адрес входа в подпрограмму помещается в регистр-счетчик команд .

- После этого, как обычно, из памяти считывается команда , адрес которой находится в счетчике команд , т.е. первая команда подпрограммы, и начинается выполнение подпрограммы.

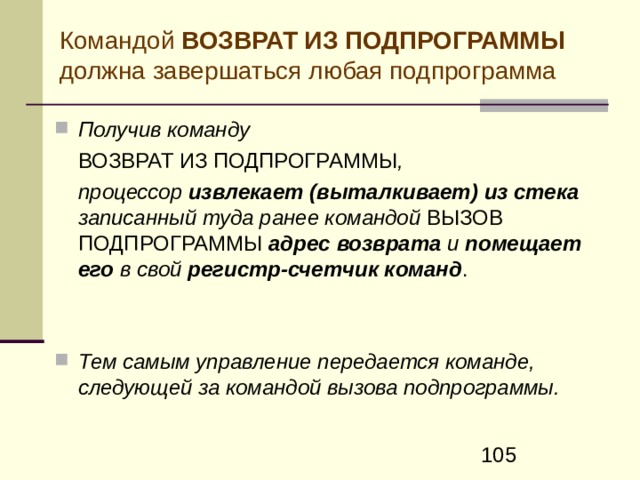

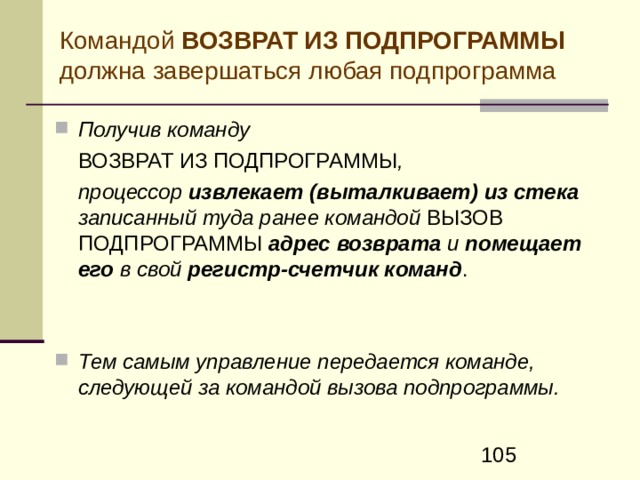

Командой ВОЗВРАТ ИЗ ПОДПРОГРАММЫ должна завершаться любая подпрограмма

ВОЗВРАТ ИЗ ПОДПРОГРАММЫ ,

процессор извлекает (выталкивает) из стека записанный туда ранее командой ВЫЗОВ ПОДПРОГРАММЫ адрес возврата и помещает его в свой регистр-счетчик команд .

- Тем самым управление передается команде, следующей за командой вызова подпрограммы.

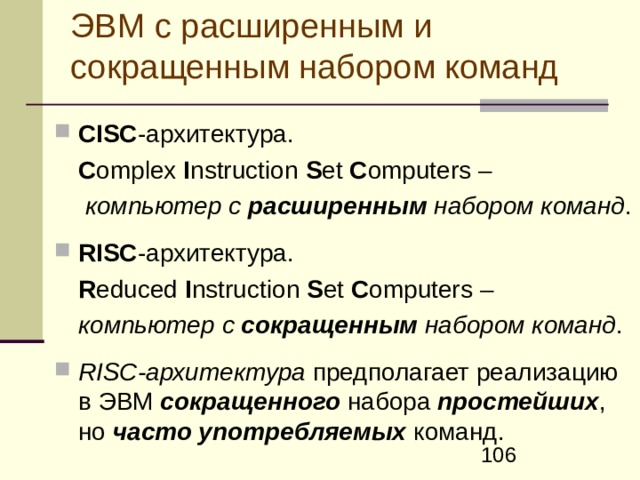

ЭВМ с расширенным и сокращенным набором команд

C omplex I nstruction S et C omputers –

компьютер с расширенным набором команд .

R educed I nstruction S et C omputers –

компьютер с сокращенным набором команд .

- RISC-архитектура предполагает реализацию в ЭВМ сокращенного набора простейших , но часто употребляемых команд.

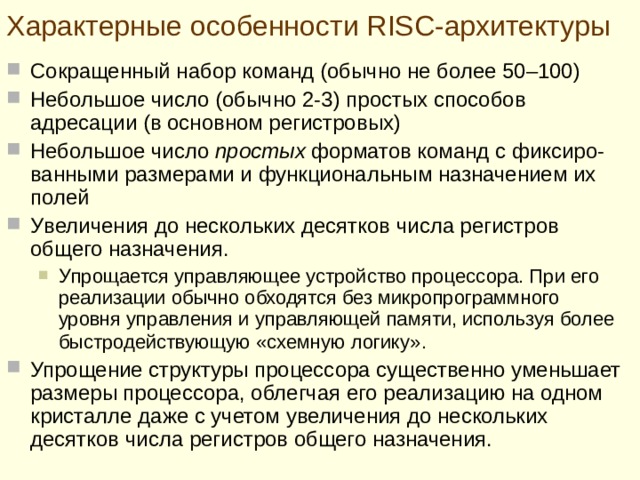

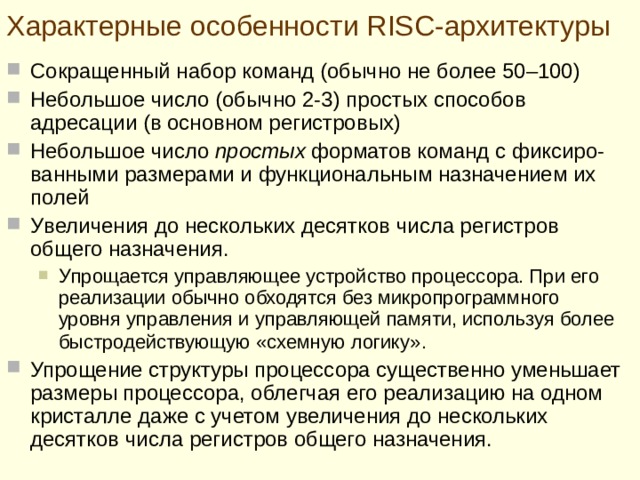

Х арактерны е особенност и RISC-архитектуры

- С окращенн ый набор команд (обычно не более 50–100)

- Н ебольшо е числ о (обычно 2-3) простых способов адресации (в основном регистров ых )

- Н ебольшо е числ о простых форматов команд с фиксиро - ванными размерами и функциональным назначением их полей

- У величения до нескольких десятков числа регистров общего назначения .

- У прощается управляющее устройство процессора. При его реализации обычно обходятся без микропрограммного уровня управления и управляющей памяти, используя более быстродействующую «схемную логику».

- У прощается управляющее устройство процессора. При его реализации обычно обходятся без микропрограммного уровня управления и управляющей памяти, используя более быстродействующую «схемную логику».

- Упрощение структуры процессора существенно уменьшает размеры процессора, облегчая его реализацию на одном кристалле даже с учетом увеличения до нескольких десятков числа регистров общего назначения.

Организация ввода-вывода. Обмен информацией с внешними устройствами

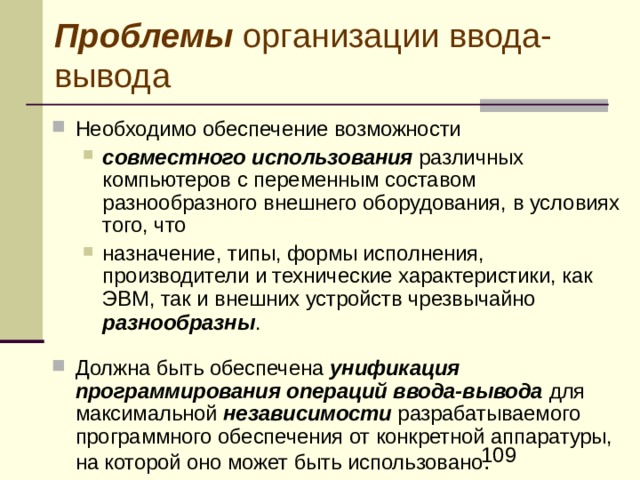

Проблемы организации ввода-вывода

- Необходимо обеспечение возможности

- совместного использования различных компьютеров с переменным составом раз нообразного внешнего оборудования, в условиях того, что назначение, типы, формы исполнения, производители и технические характеристики, как ЭВМ, так и внешних устройств чрезвычайно разнообразны .

- совместного использования различных компьютеров с переменным составом раз нообразного внешнего оборудования, в условиях того, что

- назначение, типы, формы исполнения, производители и технические характеристики, как ЭВМ, так и внешних устройств чрезвычайно разнообразны .

- Должна быть обеспечена унификация программирования операций ввода-вывода для максимальной независимости разрабатываемого программного обеспечения от конкретной аппаратуры, на которой оно может быть использовано .

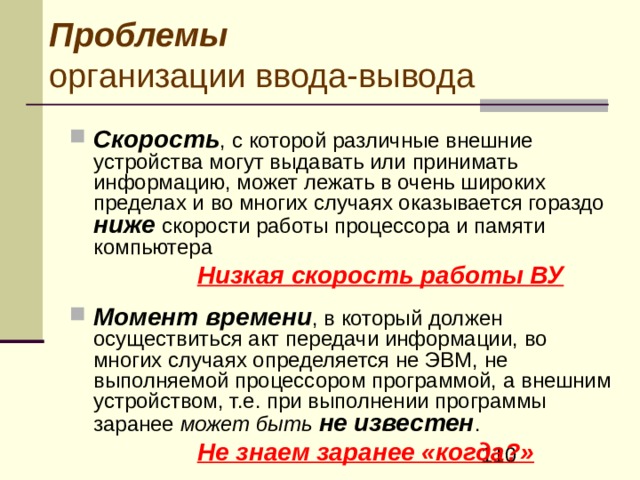

Проблемы организации ввода-вывода

- Скорость , с которой различные внешние устройства могут выдавать или принимать информацию, может лежать в очень широких пределах и во многих случаях оказывается гораздо ниже скорости работы процессора и памяти компьютера

Низкая скорость работы ВУ

- М омент времени , в который должен осуществиться акт передачи информации, во многих случаях определяется не ЭВМ, не выполняемой процессором программой, а внешним устройством, т.е. при выполнении программы заранее может быть не известен .

Не знаем заранее «когда?»

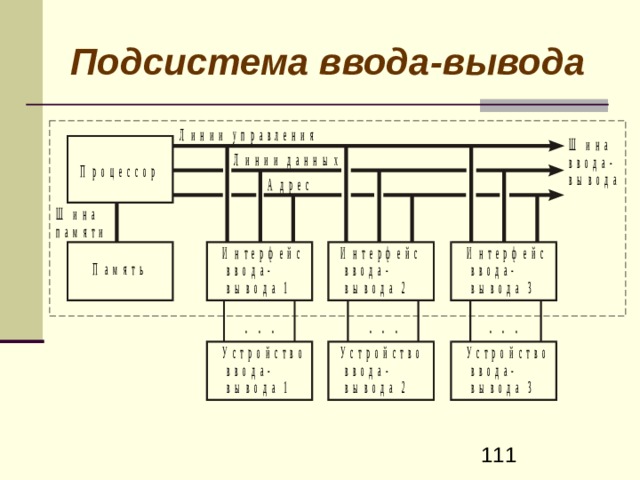

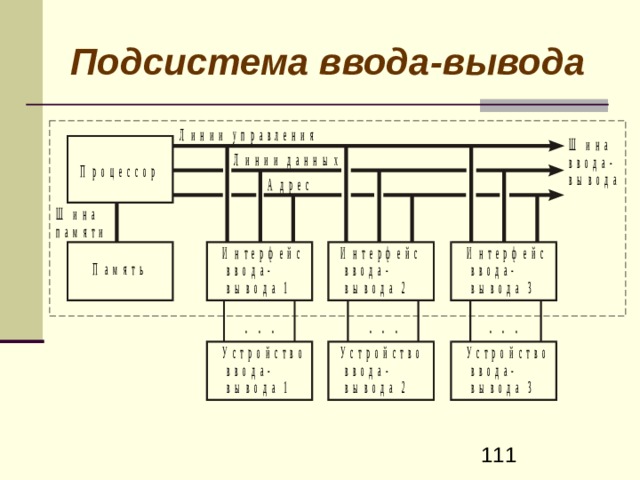

П одсистема ввода-вывода

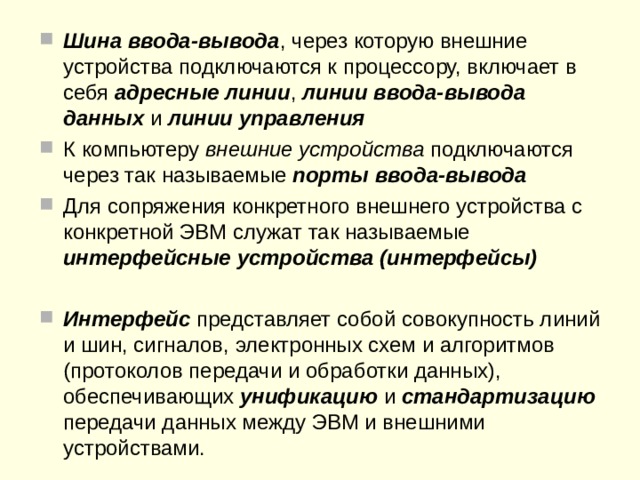

- Шина ввода-вывода , через которую внешние устройства подключаются к процессору, включает в себя адресные линии , линии ввода-вывода данных и линии управления

- К компьютеру внешние устройства подключаются через так называемые порты ввода-вывода

- Для сопряжения конкретного внешнего устройства с конкретной ЭВМ служат так называемые интерфейсные устройства (интерфейсы)

- Интерфейс представляет собой совокупность линий и шин, сигналов, электронных схем и алгоритмов (протоколов передачи и обработки данных), обеспечивающих унификацию и стандартизацию передачи данных между ЭВМ и внешними устройствами.

- Для выполняемой процессором программы порт ввода-вывода представляет собой регистр или набор регистров , содержимое которых доступно из программ ы для чтения и/или записи во время операций ввода-вывода .

- Передача (вывод) числа или кода из ЭВМ во внешнее устройство реализуется их передачей из регистра процессора или ячейки памяти в регистр данных интерфейса внешнего устройства .

- П рием (ввод) информации из внешнего устройства заключается в чтении процессором содержимого (числа или кода) регистра данных интерфейса и передача в ячейку памяти или регистр процессора .

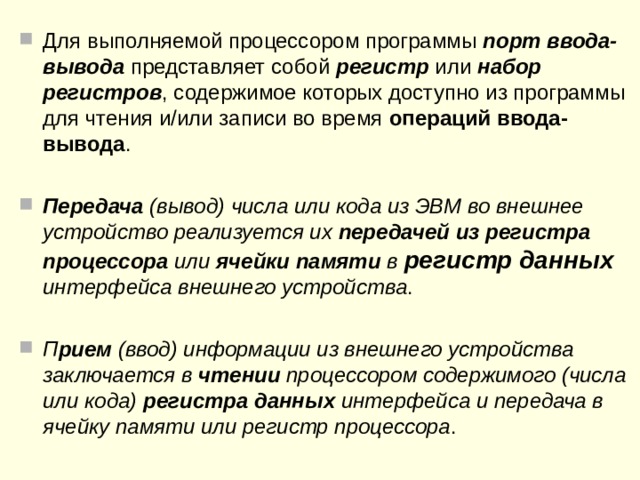

Три режима обмена информацией с внешними устройствами

- Программный обмен данными по флагу готовности внешнего устройства – это передача или прием данных

- по инициативе и под управлением программы , выполняемой центральным процессором ЭВМ.

- по инициативе и

- под управлением программы , выполняемой центральным процессором ЭВМ.

- Программный обмен данными в режиме прерывания программы .

- Инициатива обмена принадлежит внешнему устройству ,

- Инициатива обмена принадлежит внешнему устройству ,

(для этого им осуществляется прерывание выполняемой процессором программы) и затем

- (для этого им осуществляется прерывание выполняемой процессором программы) и затем

- принудительный перевод процессора на выполнение программы обслуживания внешнего устройства , затребовавшего прерывание, по окончании которой возвращение к выполнению прерванной программы.

- принудительный перевод процессора на выполнение программы обслуживания внешнего устройства , затребовавшего прерывание, по окончании которой возвращение к выполнению прерванной программы.

- Обмен данными в режиме прямого доступа к памяти (ПДП).

- У правление обменом берет на себя внешнее устройство

- У правление обменом берет на себя внешнее устройство

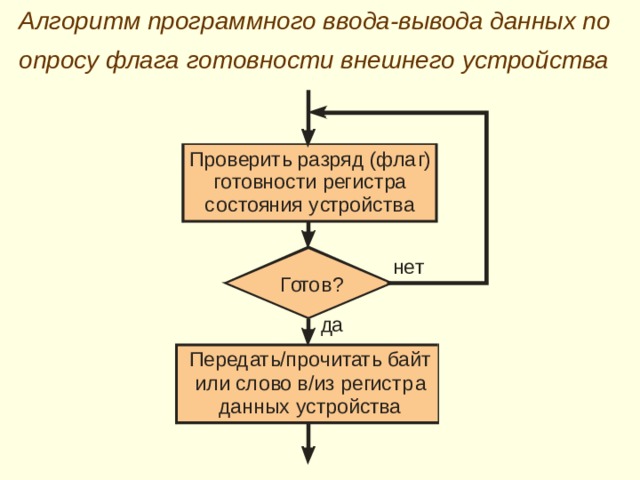

Программный режим ввода-вывода по опросу готовности внешнего устройства

- О бмен информацией между компьютером и внешними устройствами осуществляется по инициативе и под управлением выполняемой программы

Проблема

- С корость обработки информации внешним устройством, как правило, существенно ниже быстродействия процессора ,

поэтому в нешнее устройство может быть не готовым к приему или передаче информации В конкретный момент времени

Решение

- Н еобходим механизм, позволяющий программным путем определять состояние готовности или неготовности внешнего устройства к приему или передаче данных

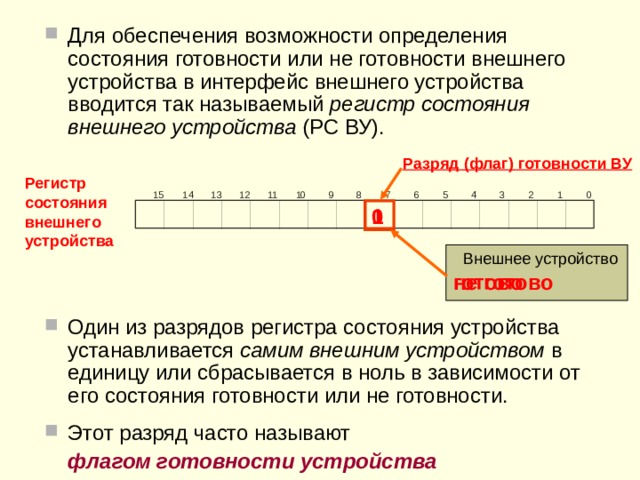

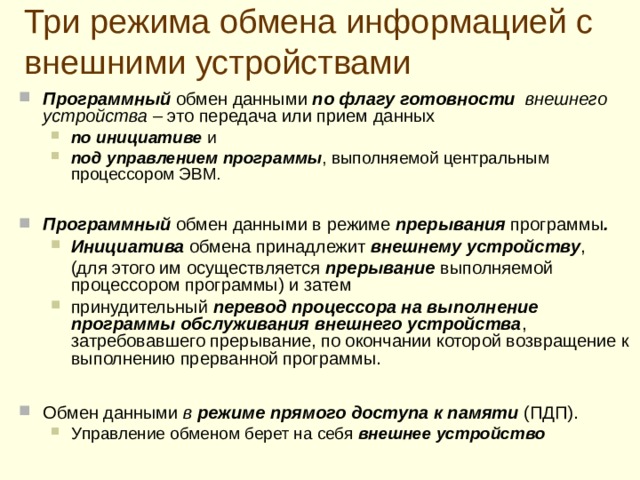

- Для обеспечения возможности определения состояния готовности или не готовности внешнего устройства в интерфейс внешнего устройства вводится так называемый регистр состояния внешнего устройства (РС ВУ).

- Один из разрядов регистра состояния устройства устанавливается самим внешним устройством в единицу или сбрасывается в ноль в зависимости от его состояния готовности или не готовности.

- Этот разряд часто называют

флагом готовности устройства

Разряд (флаг) готовности ВУ

Регистр

состояния

внешнего

устройства

0

1

Внешнее устройство

готово

не готово

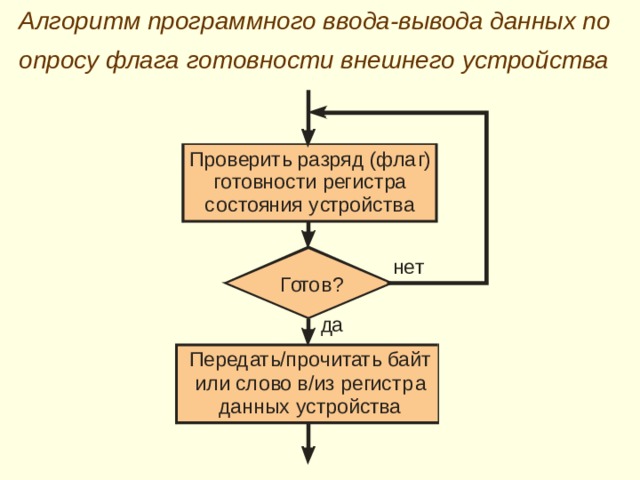

Алгоритм п рограммного ввода-вывода данных по опросу флага готовности внешнего устройства

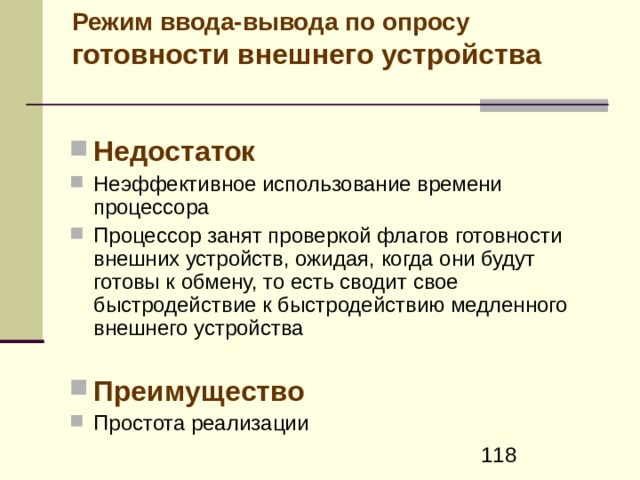

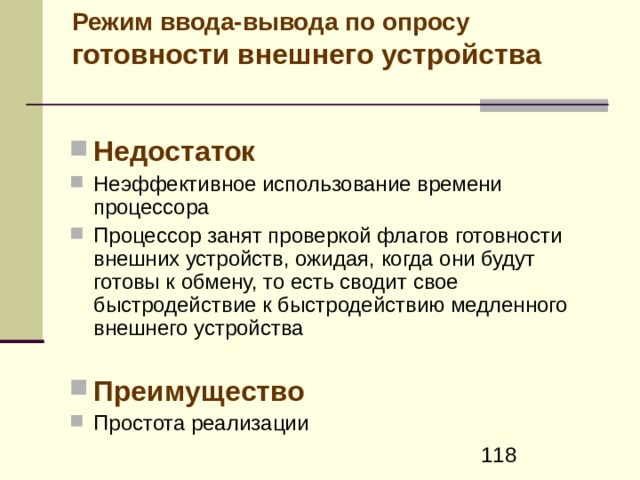

Р ежим ввода-вывода по опросу готовности внешнего устройства

- Недостаток

- Неэффективное использование времени процессора

- Процессор занят проверкой флагов готовности внешних устройств, ожидая, когда они будут готовы к обмену, то есть сводит свое быстродействие к быстродействию медленного внешнего устройства

- Преимущество

- Простота реализации

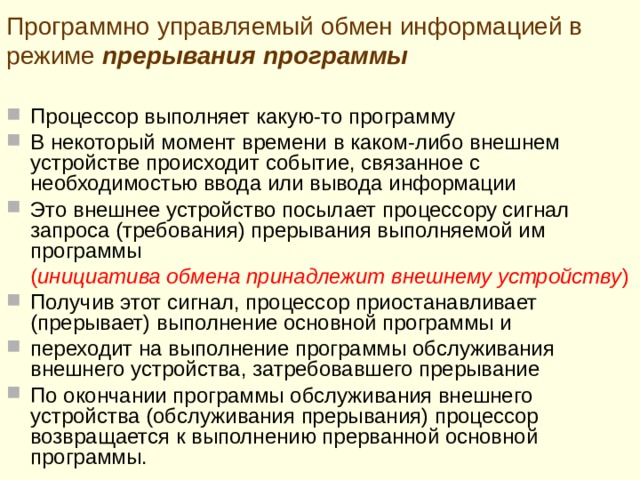

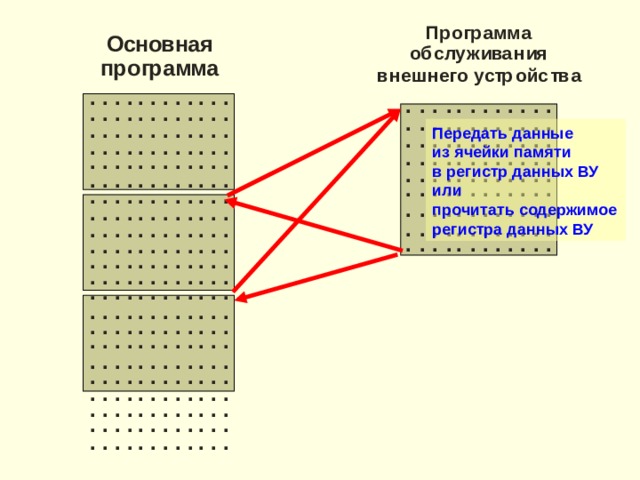

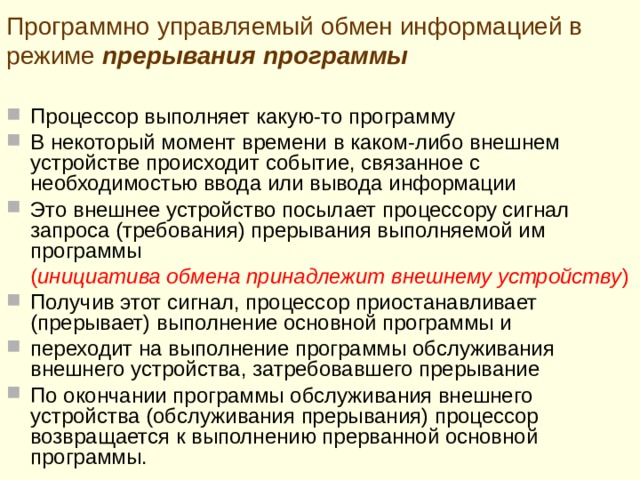

Программно управляемый обмен информацией в режиме прерывания программы

- Процессор выполняет какую-то программу

- В некоторый момент времени в каком-либо внешнем устройстве происходит событие, связанное с необходимостью ввода или вывода информации

- Это внешнее устройство посылает процессору сигнал запроса (требования) прерывания выполняемой им программы

( инициатива обмена принадлежит внешнему устройству )

- Получив этот сигнал, процессор приостанавливает (прерывает) выполнение основной программы и

- переходит на выполнение программы обслуживания внешнего устройства, затребовавшего прерывание

- По окончании программы обслуживания внешнего устройства (обслуживания прерывания) процессор возвращается к выполнению прерванной основной программы.

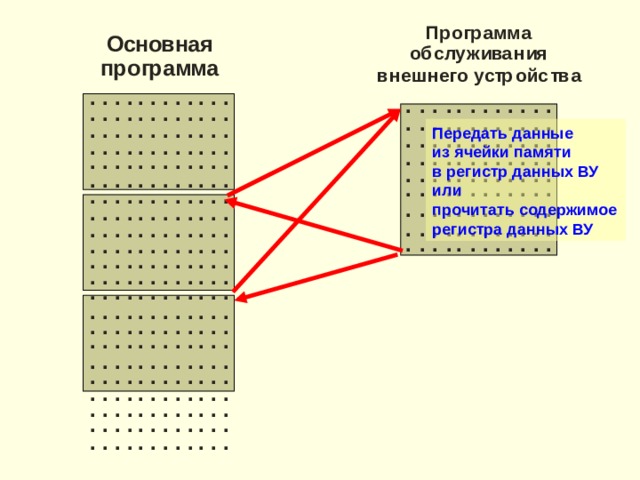

Передать данные

из ячейки памяти

в регистр данных ВУ

или

прочитать содержимое

регистра данных ВУ

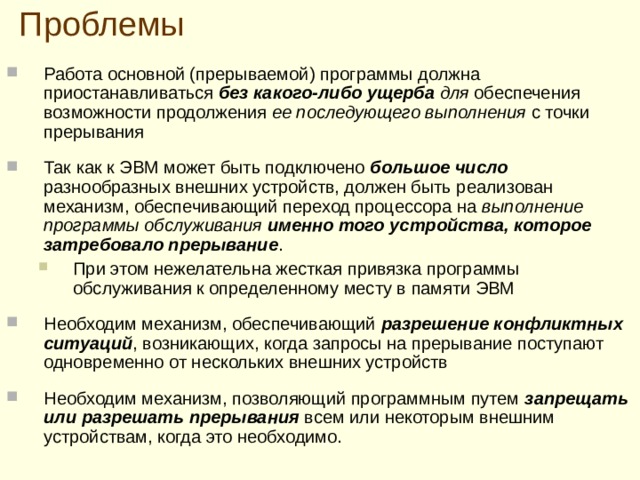

Проблемы

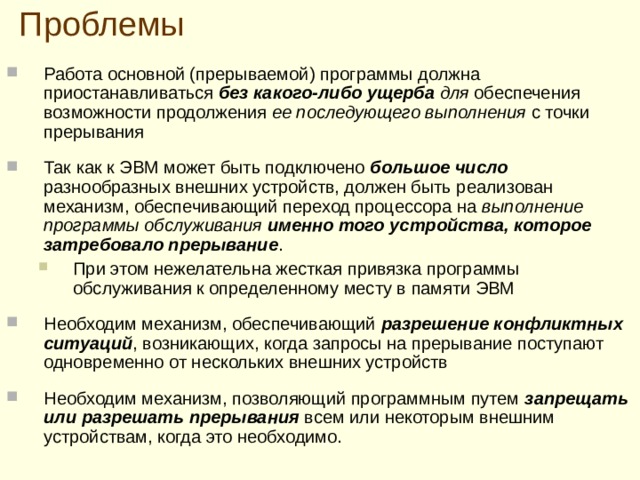

- Работа основной (прерываемой) программы должна приостанавливаться без какого-либо ущерба для обеспечения возможности продолжения ее последующего выполнения с точки прерывания

- Так как к ЭВМ может быть подключено большое число разнообразных внешних устройств, должен быть реализован механизм, обеспечивающий переход процессора на выполнение программы обслуживания именно того устройства, которое затребовало прерывание .

- При этом нежелательна жесткая привязка программы обслуживания к определенному месту в памяти ЭВМ

- При этом нежелательна жесткая привязка программы обслуживания к определенному месту в памяти ЭВМ

- Необходим механизм, обеспечивающий разрешение конфликтных ситуаций , возникающих, когда запросы на прерывание поступают одновременно от нескольких внешних устройств

- Необходим механизм, позволяющий программным путем запрещать или разрешать прерывания всем или некоторым внешним устройствам, когда это необходимо.

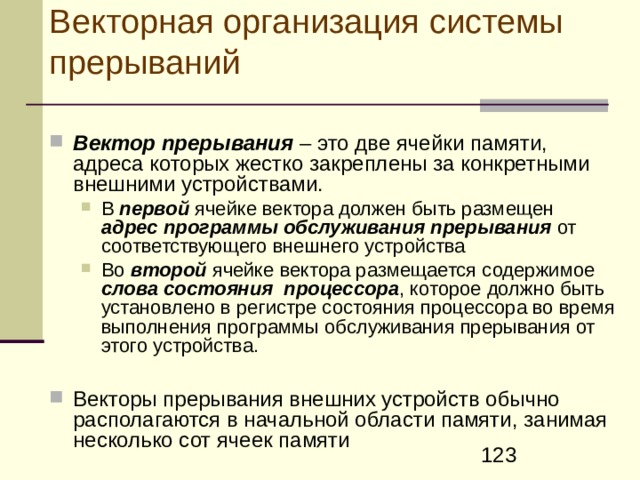

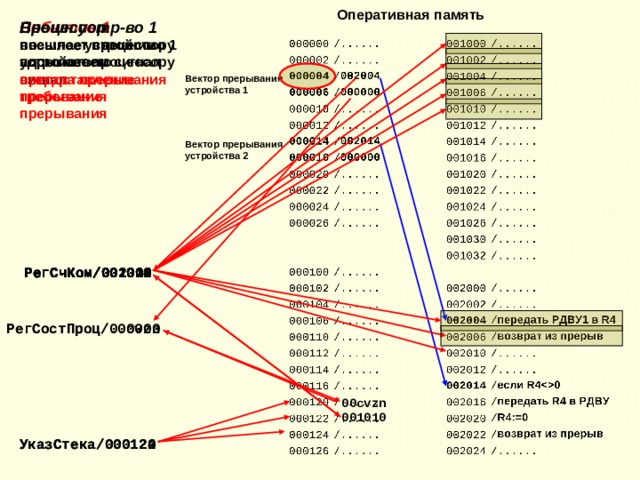

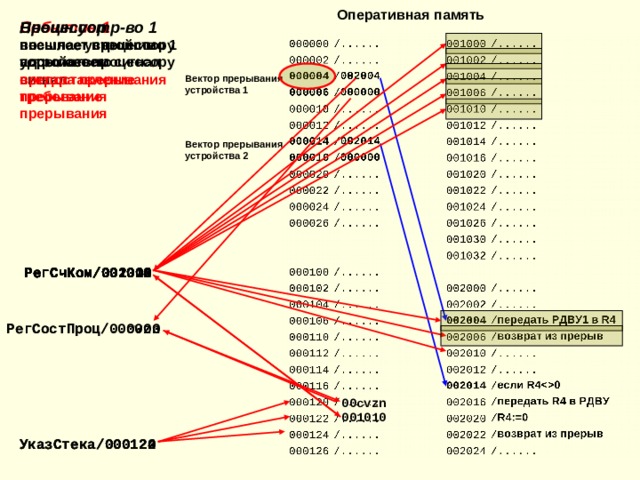

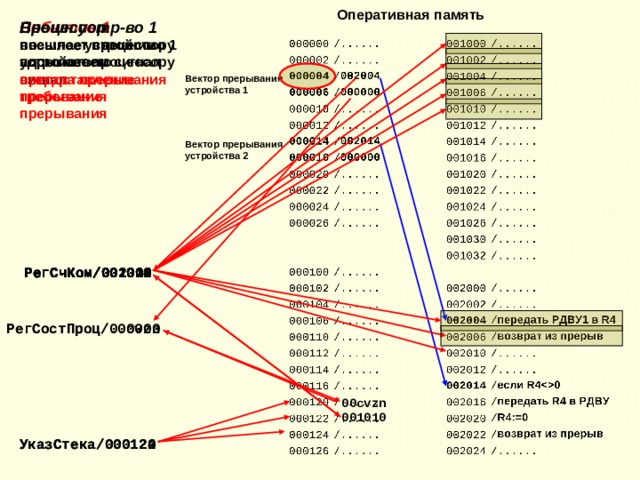

В екторн ая организаци я системы прерываний

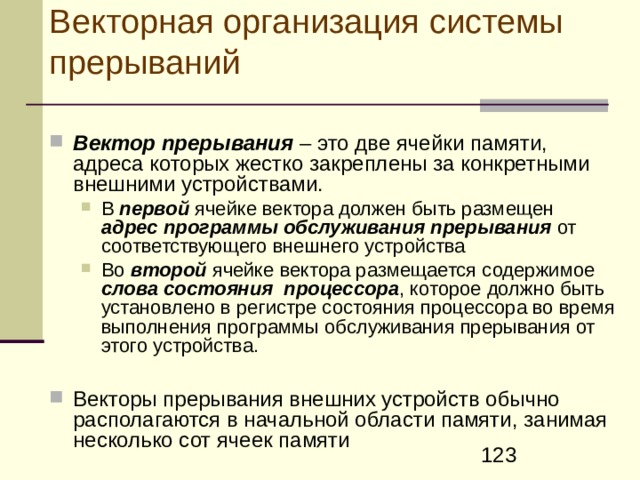

- Вектор прерывания – это две ячейки памяти, адреса которых жестко закреплены за конкретными внешними устройствами.

- В первой ячейке вектора должен быть размещен адрес программы обслуживания прерывания от соответствующего внешнего устройства Во второй ячейке вектора размещается содержимое слова состояния процессора , которое должно быть установлено в регистре состояния процессора во время выполнения программы обслуживания прерывания от этого устройства.

- В первой ячейке вектора должен быть размещен адрес программы обслуживания прерывания от соответствующего внешнего устройства

- Во второй ячейке вектора размещается содержимое слова состояния процессора , которое должно быть установлено в регистре состояния процессора во время выполнения программы обслуживания прерывания от этого устройства.

- Векторы прерывания внешних устройств обычно располагаются в начальной области памяти, занимая несколько сот ячеек памяти

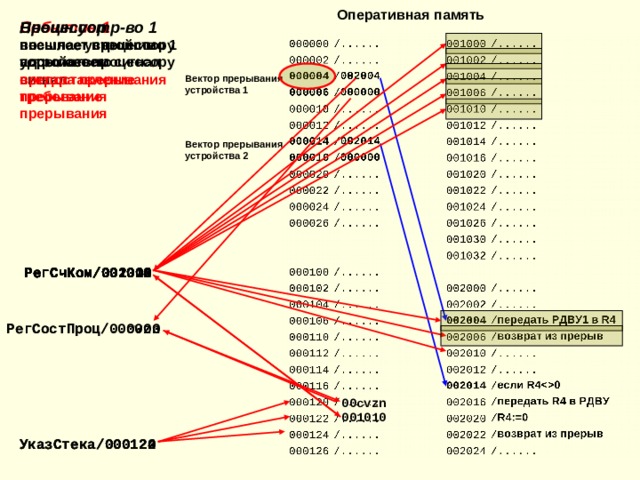

Оперативная память

Событие 1

Внешн.устр-во 1

посылает процессору

адрес своего

Процессор

посылает внешним

устройствам сигнал

внешнее устройство 1

посылает процессору

сигнал

вектора прерывания

предоставление

прерывания

требование

прерывания

Вектор прерывания

устройства 1

Вектор прерывания

устройства 2

РегСчКом / 002006

РегСчКом / 002010

РегСчКом / 001000

РегСчКом / 001010

РегСчКом / 002004

РегСчКом / 001006

РегСчКом / 001004

РегСчКом / 001002

РегСостПроц / .. cvzn

РегСостПроц / 000000

00cvzn

001010

УказСтека / 00012 2

УказСтека / 00012 4

УказСтека / 00012 0

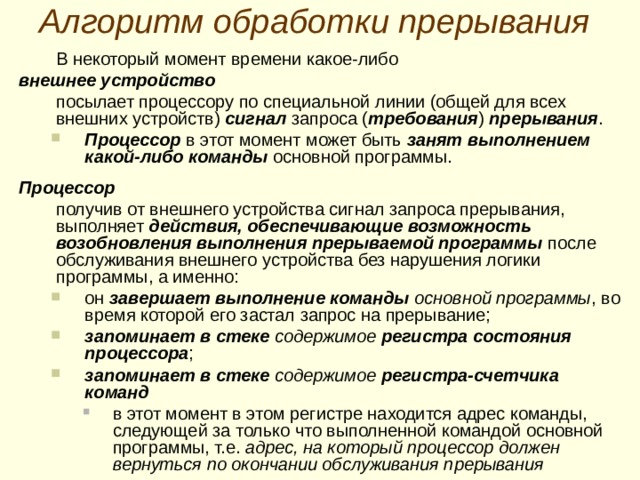

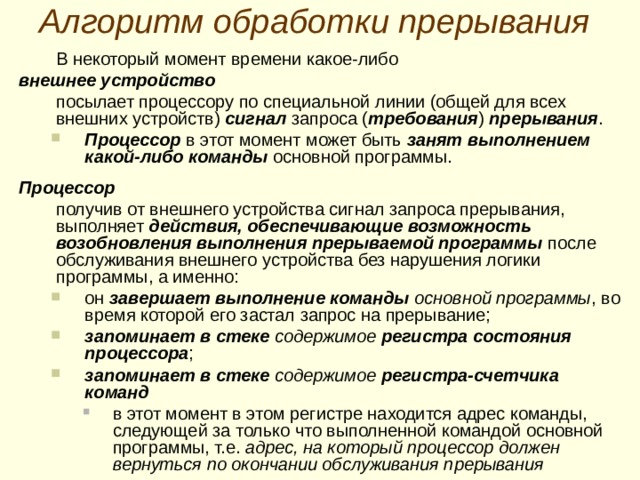

Алгоритм обработки прерывания

В некоторый момент времени какое-либо

внешнее устройство

посылает процессору по специальной линии (общей для всех внешних устройств) сигнал запроса ( требования ) прерывания .

- Процессор в этот момент может быть занят выполнением какой-либо команды основной программы.

- Процессор в этот момент может быть занят выполнением какой-либо команды основной программы.

Процессор

получив от внешнего устройства сигнал запроса прерывания, выполняет действия, обеспечивающие возможность возобновления выполнения прерываемой программы после обслуживания внешнего устройства без нарушения логики программы, а именно:

- он завершает выполнение команды основной программы , во время которой его застал запрос на прерывание; запоминает в стеке содержимое регистра состояния процессора ; запоминает в стеке содержимое регистра-счетчика команд

- он завершает выполнение команды основной программы , во время которой его застал запрос на прерывание;

- запоминает в стеке содержимое регистра состояния процессора ;

- запоминает в стеке содержимое регистра-счетчика команд

- в этот момент в этом регистре находится адрес команды, следующей за только что выполненной командой основной программы, т.е. адрес, на который процессор должен вернуться по окончании обслуживания прерывания

- в этот момент в этом регистре находится адрес команды, следующей за только что выполненной командой основной программы, т.е. адрес, на который процессор должен вернуться по окончании обслуживания прерывания

- в этот момент в этом регистре находится адрес команды, следующей за только что выполненной командой основной программы, т.е. адрес, на который процессор должен вернуться по окончании обслуживания прерывания

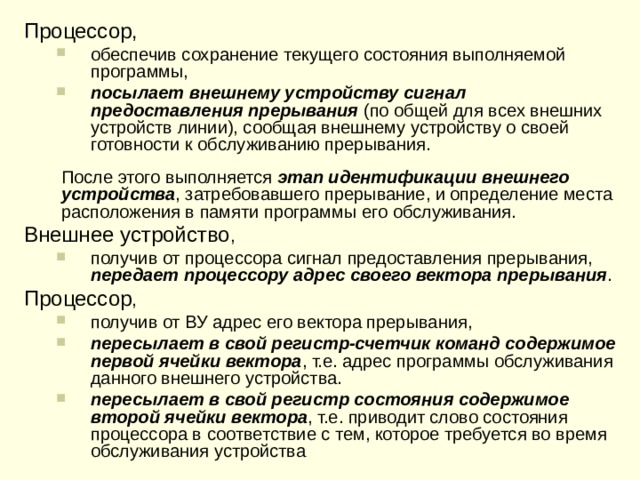

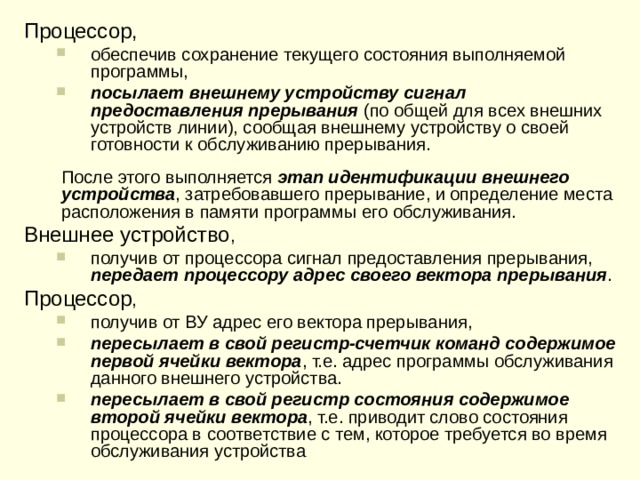

Процессор,

- обеспечив сохранение текущего состояния выполняемой программы, посылает внешнему устройству сигнал предоставления прерывания (по общей для всех внешних устройств линии), сообщая внешнему устройству о своей готовности к обслуживанию прерывания.

- обеспечив сохранение текущего состояния выполняемой программы,

- посылает внешнему устройству сигнал предоставления прерывания (по общей для всех внешних устройств линии), сообщая внешнему устройству о своей готовности к обслуживанию прерывания.

После этого выполняется этап идентификации внешнего устройства , затребовавшего прерывание, и определение места расположения в памяти программы его обслуживания.

Внешнее устройство ,

- получив от процессора сигнал предоставления прерывания, передает процессору адрес своего вектора прерывания .

- получив от процессора сигнал предоставления прерывания, передает процессору адрес своего вектора прерывания .

Процессор ,

- получив от ВУ адрес его вектора прерывания, пересылает в свой регистр-счетчик команд содержимое первой ячейки вектора , т.е. адрес программы обслуживания данного внешнего устройства. пересылает в свой регистр состояния содержимое второй ячейки вектора , т.е. приводит слово состояния процессора в соответствие с тем, которое требуется во время обслуживания устройства

- получив от ВУ адрес его вектора прерывания,

- пересылает в свой регистр-счетчик команд содержимое первой ячейки вектора , т.е. адрес программы обслуживания данного внешнего устройства.

- пересылает в свой регистр состояния содержимое второй ячейки вектора , т.е. приводит слово состояния процессора в соответствие с тем, которое требуется во время обслуживания устройства

- Перечисленные операции завершают процесс п одготовки процессора к выполнению программы обслуживания внешнего устройства , затребовавшего прерывание

- Далее, как обычно, процессор в ыбира ет из памяти для исполнения команду, адрес которой находится в его регистре-счетчике команд , т.е. первую команду программы обслуживания прерывания .

- То есть , процессор переходит к выполнени ю программы обслуживания прерывания

Выполнение программы обслуживания внешнего устройства завершается специальной командой ВОЗВРАТ ИЗ ПРЕРЫВАНИЯ

- Получив команду ВОЗВРАТ ИЗ ПРЕРЫВАНИЯ, завершающую программу обслуживания,

процессор

- выталкивает из стека сохраненный там адрес ячейки основной программы , на которую ему надо вернуться из прерывания, и

- пересылает его в свой регистр-счетчик команд , затем

- выталкивает из стека прежнее слово состояния процессора и

- записывает его в свой регистр состояния ,

- полностью восстанавливая тем самым свое состояние, имевшее место до перехода к обслуживанию прерывания.

- полностью восстанавливая тем самым свое состояние, имевшее место до перехода к обслуживанию прерывания.

Таким образом п роцессор возобновляет выполнение прерванной программы

Оперативная память

Событие 1

Внешн.устр-во 1

посылает процессору

адрес своего

Процессор

посылает внешним

устройствам сигнал

внешнее устройство 1

посылает процессору

сигнал

вектора прерывания

предоставление

прерывания

требование

прерывания

Вектор прерывания

устройства 1

Вектор прерывания

устройства 2

РегСчКом / 002006

РегСчКом / 002010

РегСчКом / 001000

РегСчКом / 001010

РегСчКом / 002004

РегСчКом / 001006

РегСчКом / 001004

РегСчКом / 001002

РегСостПроц / .. cvzn

РегСостПроц / 000000

00cvzn

001010

УказСтека / 00012 2

УказСтека / 00012 4

УказСтека / 00012 0

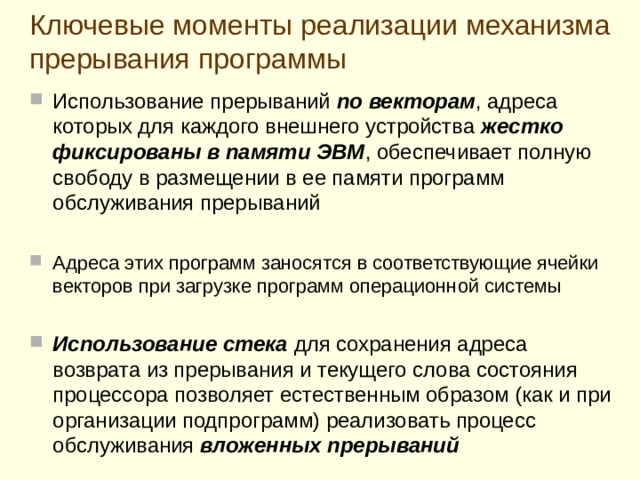

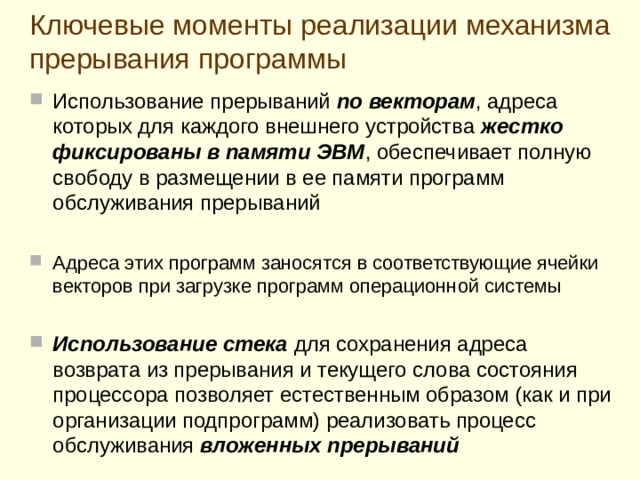

Ключевые моменты реализации механизма прерывания программы

- Использование прерываний по векторам , адреса которых для каждого внешнего устройства жестко фиксированы в памяти ЭВМ , обеспечивает полную свободу в размещении в ее памяти программ обслуживания прерываний

- Адреса этих программ заносятся в соответствующие ячейки векторов при загрузке программ операционной системы

- Использование стека для сохранения адреса возврата из прерывания и текущего слова состояния процессора позволяет естественным образом (как и при организации подпрограмм) реализовать процесс обслуживания вложенных прерываний

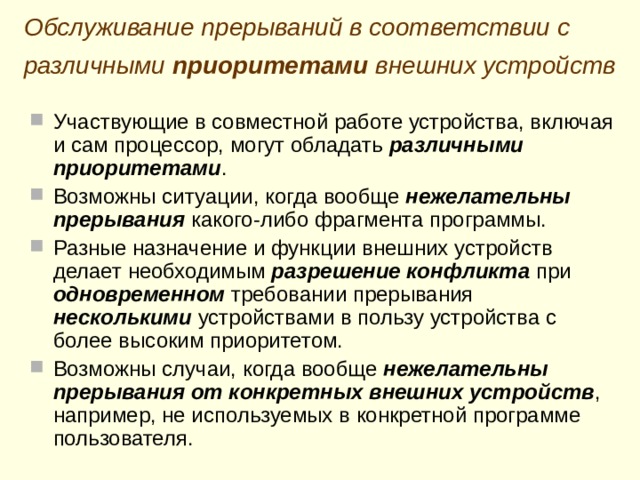

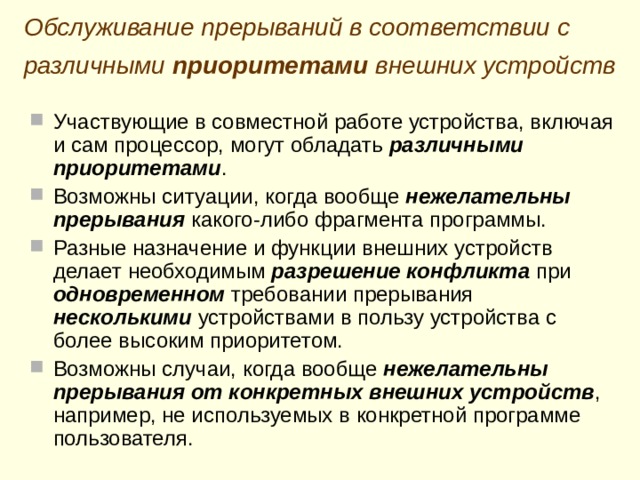

О бслуживание прерываний в соответствии с различными приоритетами внешних устройств

- У частвующие в совместной работе устройства, включая и сам процессор, могут обладать различными приоритетами .

- Возможны ситуации, когда вообще нежелательны прерывания какого-либо фрагмента программы.

- Разные назначение и функции внешних устройств делает необходимым разрешение конфликта при одновременном требовании прерывания несколькими устройствами в пользу устройства с более высоким приоритетом.

- Возможны случаи, когда вообще нежелательны прерывания от конкретных внешних устройств , например, не используемых в конкретной программе пользователя.

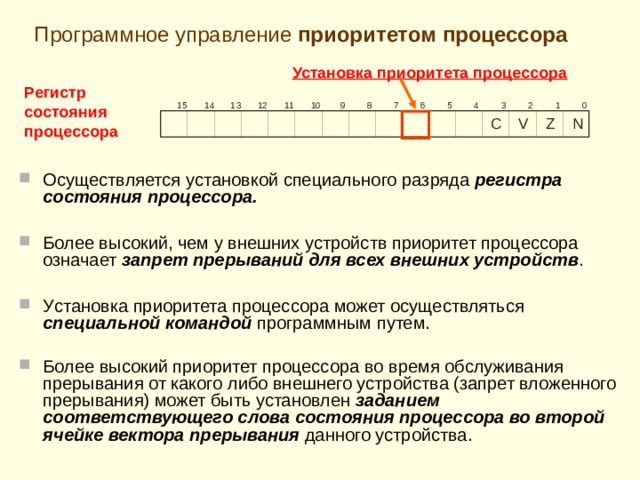

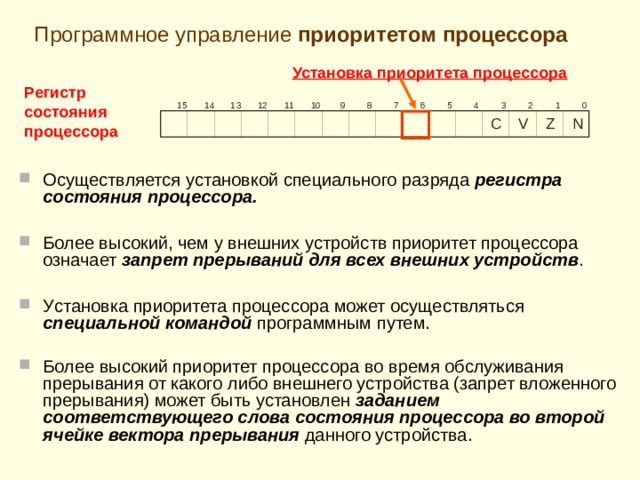

П рограммно е управлени е приоритетом процессора

Установка приоритета процессора

Регистр

состояния

процессора

- Осуществляется у становк ой специального разряда регистра состояния процессора.

- Более высокий, чем у внешних устройств приоритет процессора означает запрет прерываний для всех внешних устройств .

- У становка приоритета процессора может осуществляться специальной командой программным путем.

- Б олее высокий приоритет процессора во время обслуживания прерывания от какого либо внешнего устройства (запрет вложенного прерывания) может быть установлен заданием соответствующего слов а состояния процессора во второй ячейке вектора прерывания данного устройства .

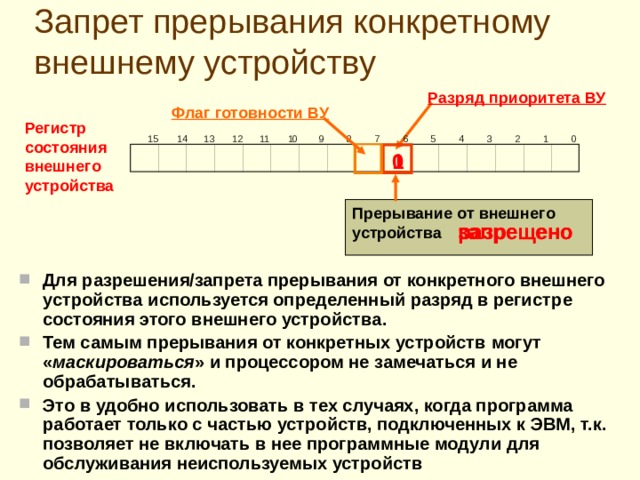

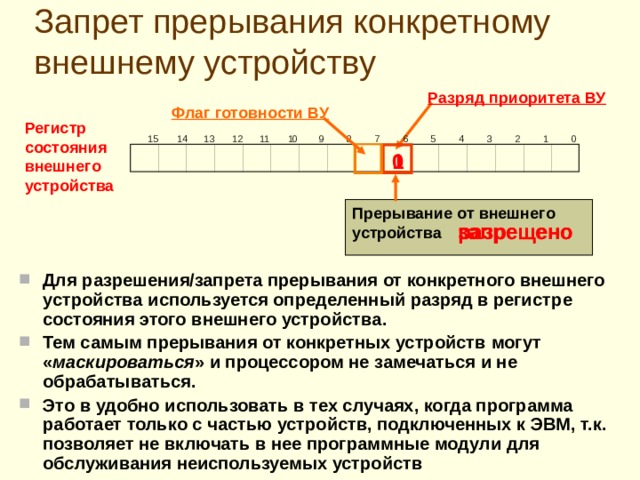

З апрет прерывания конкретн ому внешн ему устройств у

Разряд приоритета ВУ

Флаг готовности ВУ

Регистр

состояния

внешнего

устройства

0

1

Прерывание от внешнего

устройства

разрешено

запрещено

- Для разрешения/запрета прерывания от конкретного внешнего устройства используется определенный разряд в регистр е состояния этого внешн его устройств а .

- Тем самым прерывания от конкретных устройств могут « маскир оваться » и процессором не замеча ться и не обрабатываться .

- Это в удобно использовать в тех случаях, когда программа работает только с частью устройств, подключенных к ЭВМ, т.к. позволяет не включать в нее программные модули для обслуживания неиспользуемых устройств

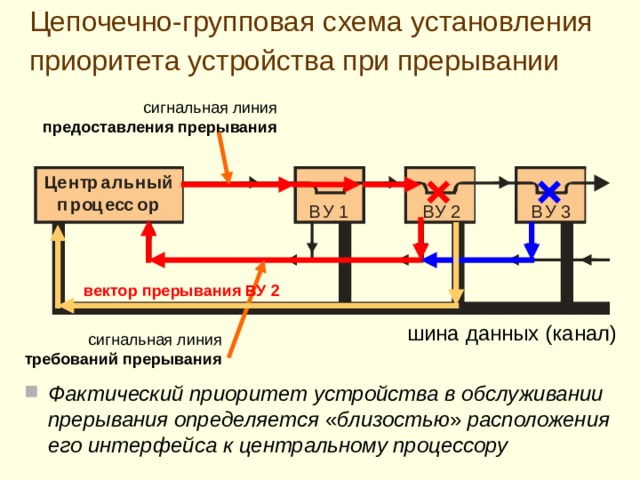

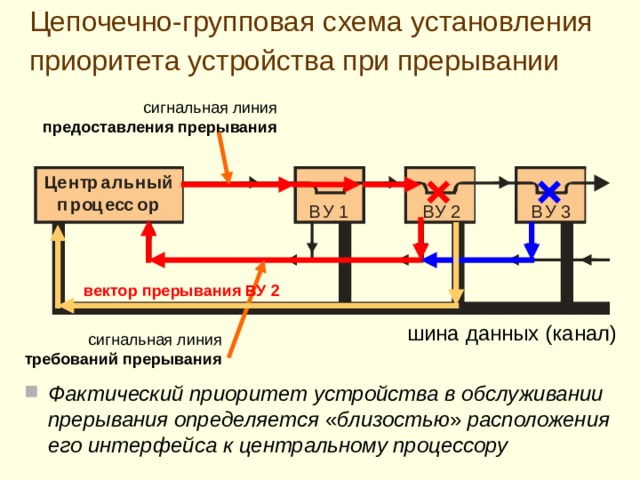

Ц епочечно-групповая схема установления приоритета устройства при прерывании

сигнальная линия

предоставления прерывания

вектор прерывания ВУ 2

шина данных (канал)

сигнальная линия

требований прерывания

- Фактический приоритет устройства в обслуживании прерывания определя е тся « близостью » расположения его интерфейса к центральному процессору

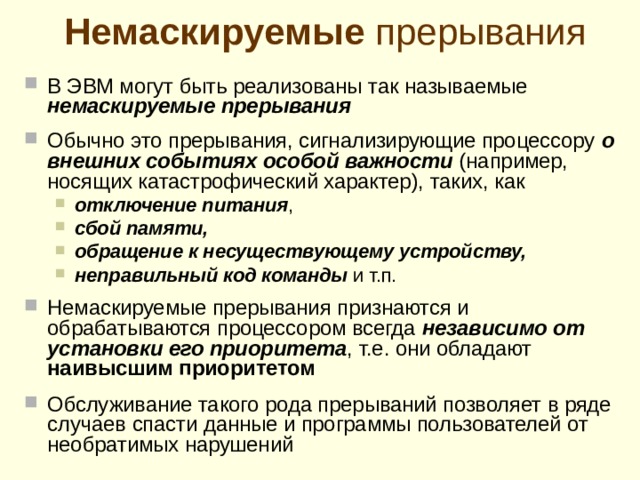

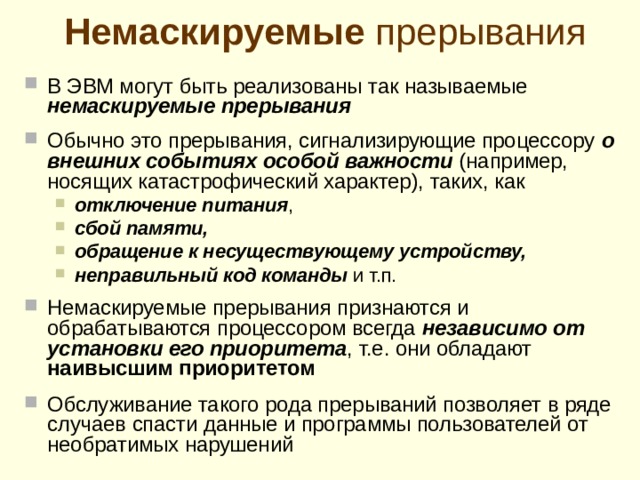

Немаскируемые прерывания

- В ЭВМ могут быть реализованы так называемые немаскируемые прерывания

- Обычно это прерывания, сигнализирующие процессору о внешних событиях особой важности (например, носящих катастрофический характер), таких, как

- отключение питания , сбой памяти, обращение к несуществующему устройству, неправильный код команды и т.п.

- отключение питания ,

- сбой памяти,

- обращение к несуществующему устройству,

- неправильный код команды и т.п.

- Немаскируемые прерывания признаются и обрабатываются процессором всегда независимо от установки его приоритета , т.е. они обладают наивысшим приоритетом

- Обслуживание такого рода прерываний позволяет в ряде случаев спасти данные и программы пользователей от необратимых нарушений

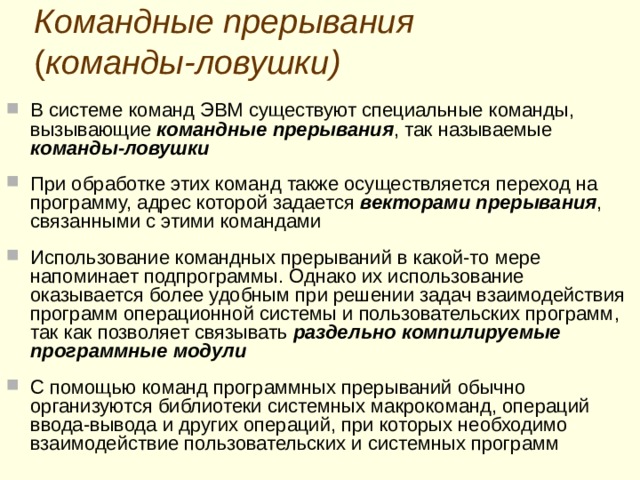

К омандные прерывания ( команды-ловушки )

- В системе команд ЭВМ существуют специальные команды, вызывающие командные прерывания , так называемые команды-ловушки

- При обработке этих команд также осуществляется переход на программу, адрес которой задается векторами прерывания , связанными с этими командами

- Использование командных прерываний в какой-то мере напоминает подпрограммы. Однако их использование оказывается более удобным при решении задач взаимодействия программ операционной системы и пользовательских программ , так как позволяет связывать раздельно компилируемые программные модули

- С помощью команд программных прерываний обычно организуются библиотеки системных макрокоманд, операций ввода-вывода и других операций, при которых необходимо взаимодействие пользовательских и системных программ

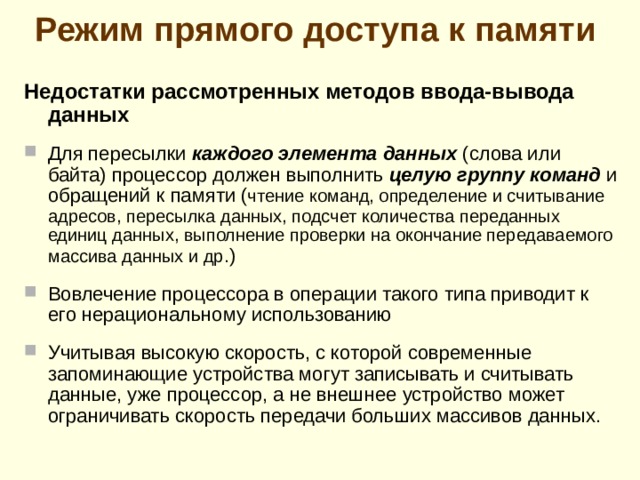

Режим п рямо го доступ а к памяти

Недостатки рассмотренных методов ввода-вывода данных

- Д ля пересылки каждого элемента данных (слова или байта) процессор должен выполнить целую группу команд и обращений к памяти ( чтение команд, определение и считывание адресов, пересылка данных, подсчет количества переданных единиц данных, выполнение проверки на окончание передаваемого массива данных и др .)

- В овлечение процессора в операции такого типа приводит к его нерациональному использованию

- У читывая высокую скорость, с которой современные запоминающие устройства могут записывать и считывать данные, уже процессор, а не внешнее устройство может ограничивать скорость передачи больших массивов данных.

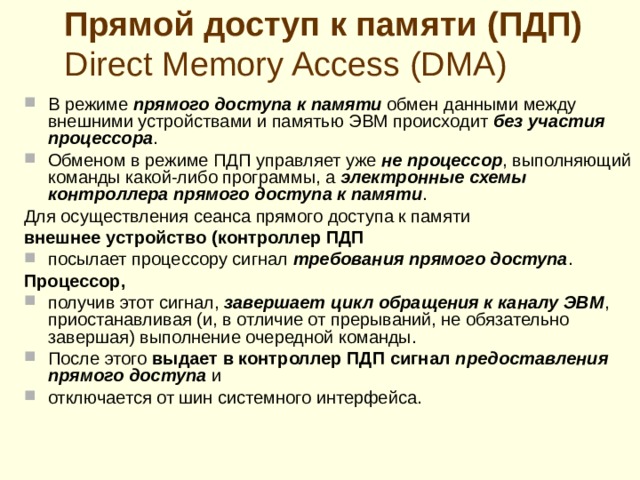

Прямой доступ к памяти (ПДП) Direct Memory Access (DMA)

- В режиме прямого доступа к памяти обмен данными между внешними устройствами и памятью ЭВМ происходит без участия процессора .

- Обменом в режиме ПДП управляет уже не процессор , выполняющий команды какой-либо программы, а электронные схемы контроллера прямого доступа к памяти .

Для осуществления сеанса прямого доступа к памяти

внешнее устройство ( контроллер ПДП

- посылает процессору сигнал требовани я прямого доступа .

Процессор,

- получив этот сигнал, завершает цикл обращения к каналу ЭВМ , приостанавливая (и, в отличие от прерываний, не обязательно завершая) выполнение очередной команды.

- После этого выдает в контроллер ПДП сигнал предоставлени я прямого доступа и

- отключается от шин системного интерфейса.

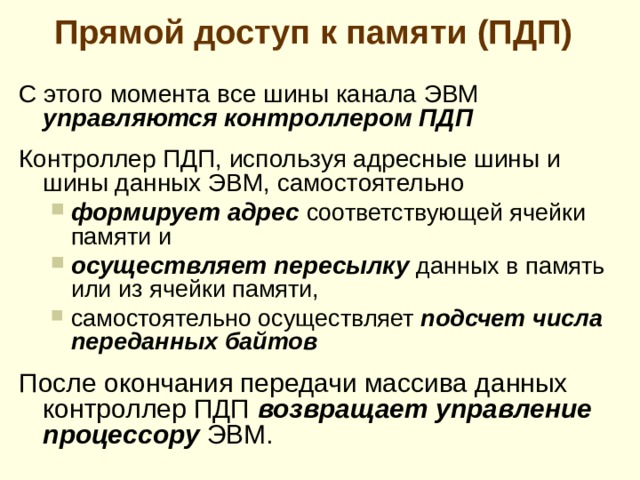

Прямой доступ к памяти (ПДП)

С этого момента все шины канала ЭВМ управляются контроллером ПДП

Контроллер ПДП, используя адресные шины и шины данных ЭВМ, самостоятельно

- формирует адрес соответствующей ячейки памяти и осуществляет пересылку данных в память или из ячейки памяти, самостоятельно осуществляет подсчет числа переданных байтов

- формирует адрес соответствующей ячейки памяти и

- осуществляет пересылку данных в память или из ячейки памяти,

- самостоятельно осуществляет подсчет числа переданных байтов

П осле окончания передачи массива данных контроллер ПДП возвращает управление процессору ЭВМ.

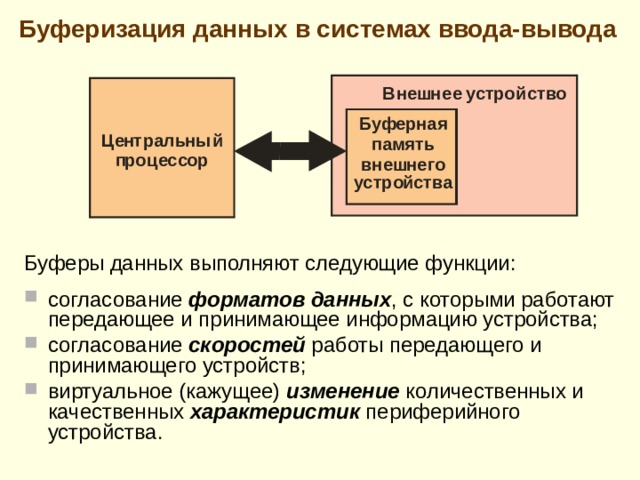

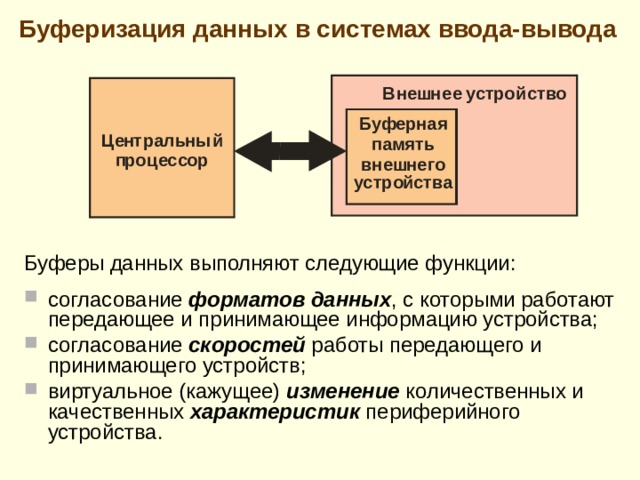

Буфер изация данных в системах ввода-вывода

Буферы данных выполняют следующие функции:

- согласование форматов данных , с которыми работают передающее и принимающее информацию устройства;

- согласование скоростей работы передающего и принимающего устройств;

- виртуальное (кажущее) изменение количественных и качественных характеристик периферийного устройства.

Буфер изация данных в системах ввода-вывода

- Наличие буфера может приводить к виртуальному (кажущемуся) качественному изменению характеристик внешнего устройства

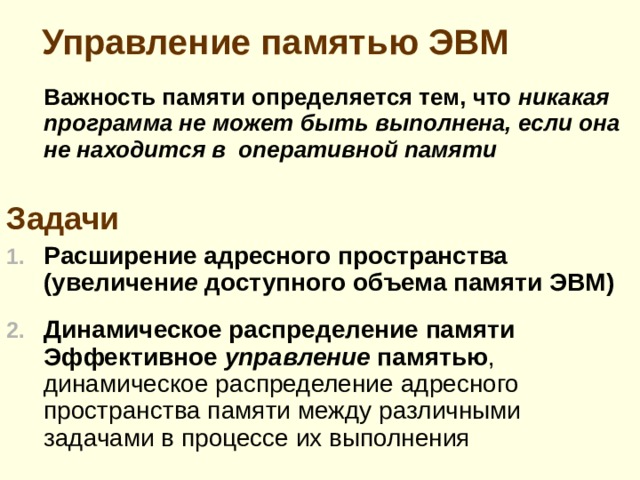

Управление памятью ЭВМ

Важность памяти определяется тем, что никакая программа не может быть выполнена, если она не находится в оперативной памяти

Задачи

- Р асширение адресного пространства (у величени е доступного объема памяти ЭВМ )

- Д инамическое распределение памяти Э ффективно е управлени е памятью , динамическо е распределени е адресного пространства памяти между различными задачами в процессе их выполнения

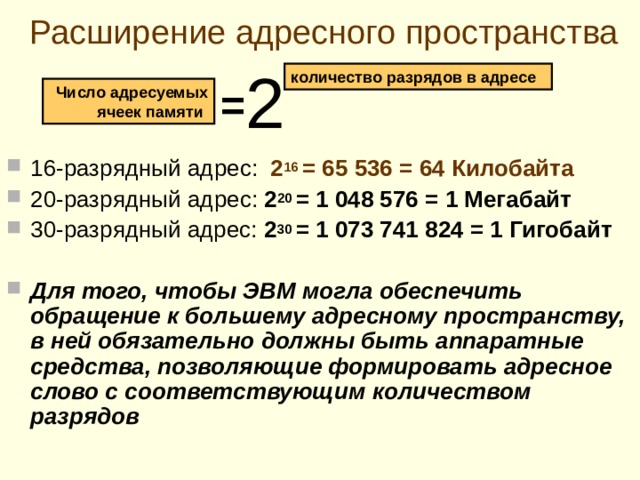

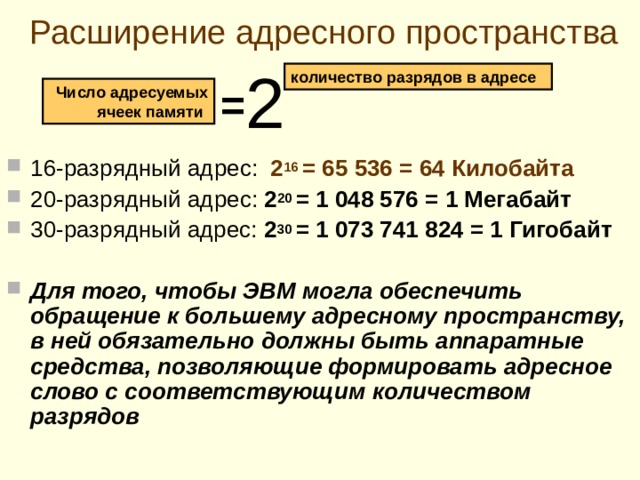

Расширение адресного пространства

2

количество разрядов в адресе

=

Число адресуемых ячеек памяти

- 16-разрядн ый адрес: 2 16 = 65 536 = 64 Килобайта

- 20 -разрядн ый адрес: 2 20 = 1 048 576 = 1 Мегабайт

- 30-разрядный адрес: 2 30 = 1 073 741 824 = 1 Гигобайт

- Для того, чтобы ЭВМ могла обеспечить обращение к большему адресному пространству, в ней обязательно должны быть аппаратные средства, позволяющие формировать адресное слово с соответствующим количеством разрядов

Физическое и виртуальное адресные пространства

- К онцепция разделения физического и виртуального адресных пространств

- Под физической памятью понимают множество имеющихся в аппаратуре ЭВМ ячеек оперативной памяти

- Виртуальной памятью называют адресное пространство, с которым оперирует пользователь в своих программах

- К онцепция выделения двух видов памяти – физической и виртуальной подразумевает, что в общем случае используемые программой физические и виртуальные адреса не совпадают

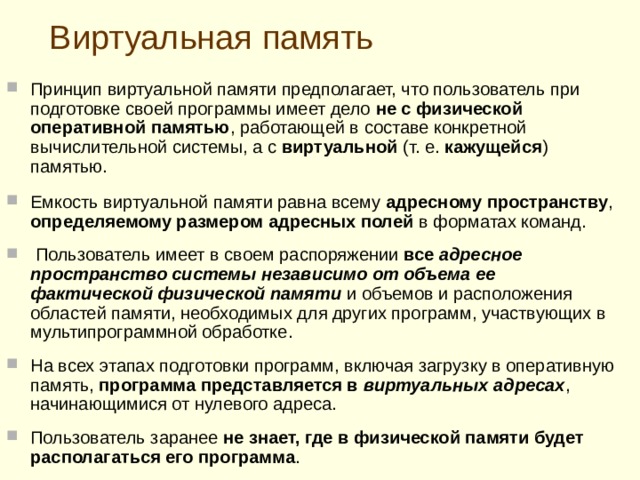

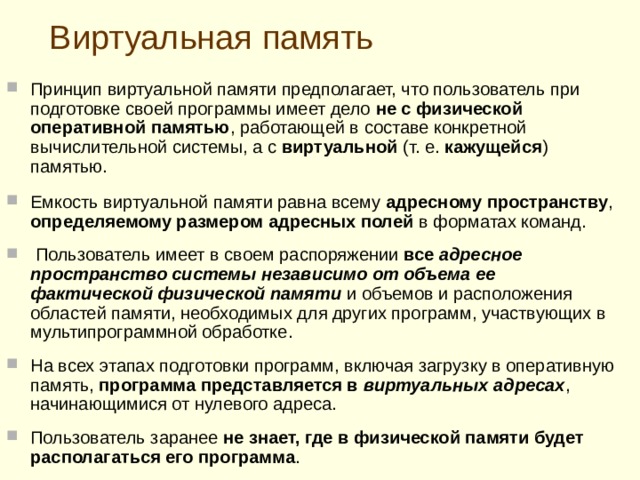

Виртуальная память

- Принцип виртуальной памяти предполагает, что пользователь при подготовке своей программы имеет дело не с физической оперативной памятью , работающей в составе конкретной вычислительной системы, а с виртуальной (т. е. кажущейся ) памятью.

- Емкость виртуальной памяти равна всему адресному пространству , определяемому размером адресных полей в форматах команд.

- Пользователь имеет в своем распоряжении все адресное пространство системы независимо от объема ее фактической физической памяти и объемов и расположения областей памяти, необходимых для других программ, участвующих в мультипрограммной обработке.

- На всех этапах подготовки программ, включая загрузку в оперативную память, программа представляется в виртуальных адресах , начинающимися от нулевого адреса.

- Пользователь заранее не знает, где в физической памяти будет располагаться его программа .

Виртуальная физическая

- При самом исполнении машинной команды с помощью специальных аппаратных и системных программных средств производится преобразование виртуальных адресов в реальные адреса действующей памяти .

- Эти средства осуществляют отображение виртуальных адресов одной или нескольких программ на конкретные адреса физической памяти , отображение.

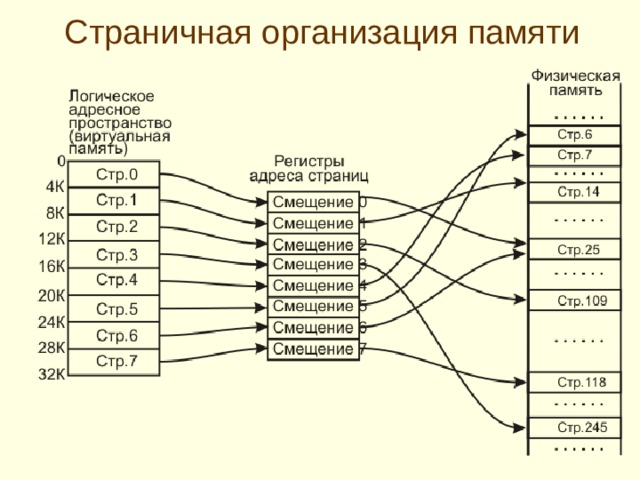

Страницы

- Преобразование виртуальных адресов в физические упрощается, если физическую и виртуальную память разбить на блоки, содержащие одинаковое число байт.

- Такие блоки обычно называются страницами или сегментами .

- Страницам виртуальной и физической памяти присваивают номера, называемые номерами соответствующих виртуальных и физических страниц.

- Каждая физическая страница способна хранить одну из виртуальных страниц.

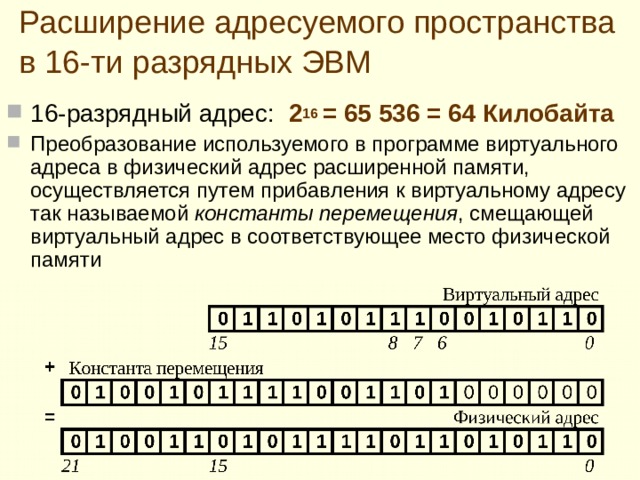

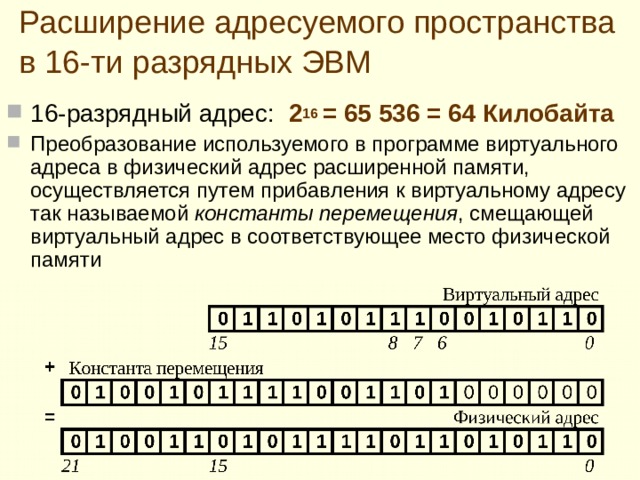

Расширение адресуемого пространства в 16-ти разрядных ЭВМ

- 16-разрядн ый адрес: 2 16 = 65 536 = 64 Килобайта

- П реобразование используемого в программе виртуального адреса в физический адрес расширенной памяти, осуществляется путем прибавления к виртуальному адресу так называемой константы перемещения , смещающей виртуальный адрес в соответствующее место физической памяти

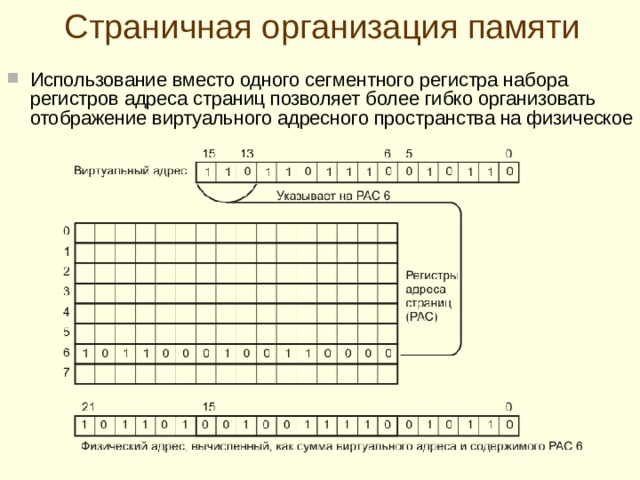

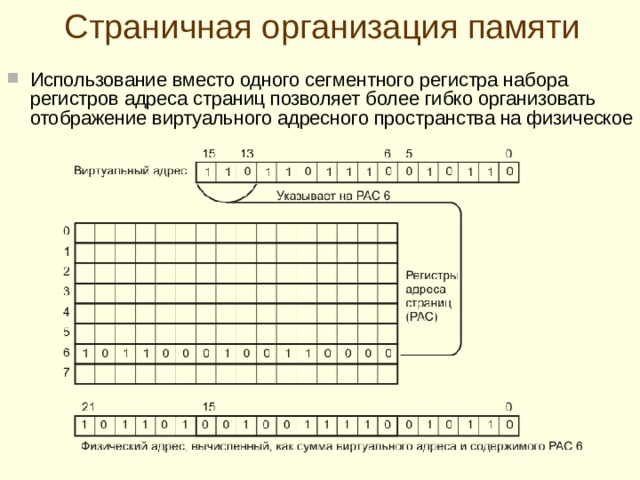

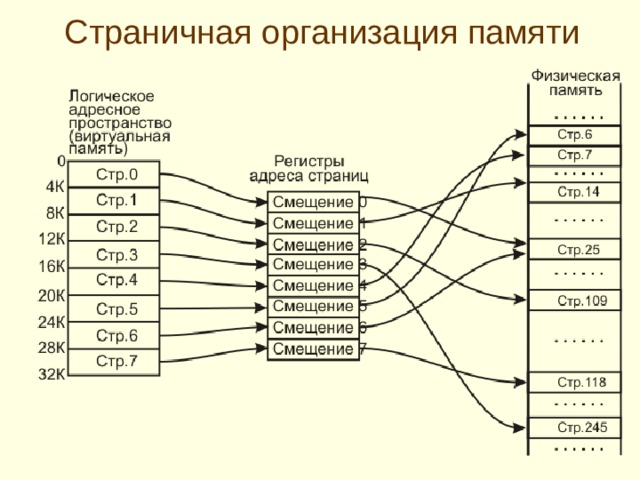

Страничная организация памяти

- Использование вместо одного сегментного регистра набора регистров адреса страниц позволяет более гибко организовать отображение виртуального адресного пространства на физическое

Страничная организация памяти

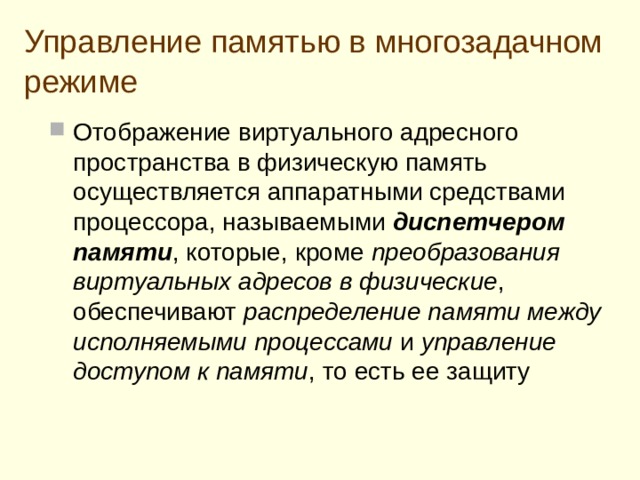

Управление памятью в многозадачном режиме

- Отображение виртуального адресного пространства в физическую память осуществляется аппаратными средствами процессора, называемыми диспетчером памяти , которые, кроме преобразования виртуальных адресов в физические , обеспечивают распределение памяти между исполняемыми процессами и управление доступом к памяти , то есть ее защиту

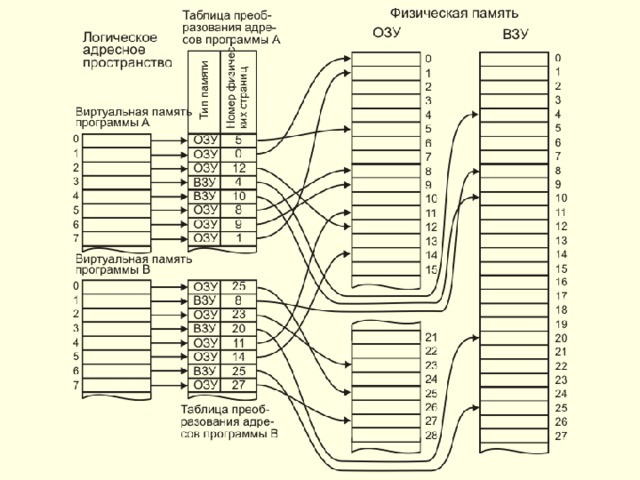

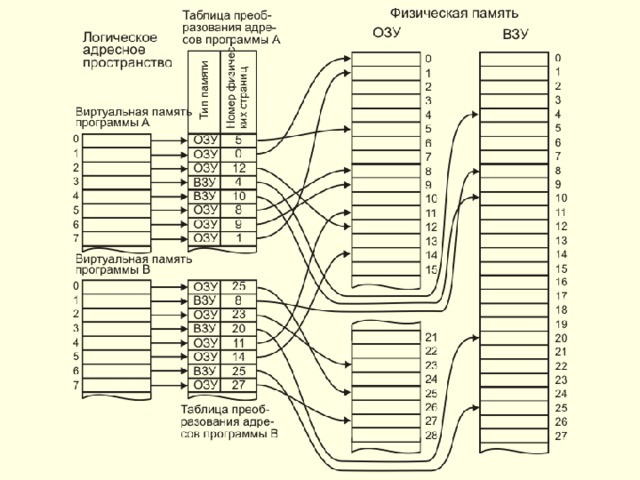

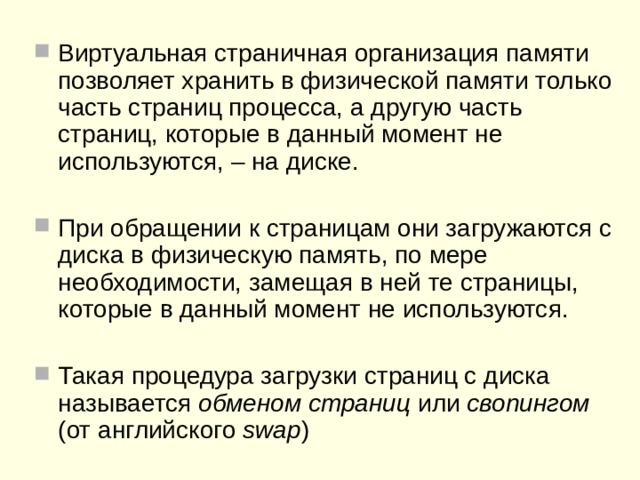

- Виртуальная страничная организация памяти позволяет хранить в физической памяти только часть страниц процесса, а другую часть страниц, которые в данный момент не используются, – на диске.

- При обращении к страницам они загружаются с диска в физическую память, по мере необходимости, замещая в ней те страницы, которые в данный момент не используются.

- Такая процедура загрузки страниц с диска называется обменом страниц или свопингом (от английского swap )

- Для каждой из программ, обрабатываемых в мультипрограммном режиме, организуется своя виртуальная память и создается своя страничная таблица, при этом все программы делят между собой одну общую физическую память.

- Страничные таблицы программ хранятся в оперативной памяти.

- Обращение к нужной строке активной страничной таблицы в оперативной памяти происходит по адресу , который определяется номером активной программы и номером виртуальной страницы

Согласование быстродействия процессора и памяти ЭВМ . Кэш-память

- Буферизация памяти состоит в использовании буферных памятей небольшой емкости, существенно более быстродействующих, чем оперативная память, включенных между процессором и основной оперативной памятью.

- Буферные памяти скрыты от программиста в том смысле, что он не может их адресовать и может даже не знать об их существовании .

- Такого рода запоминающие устройства получили название кэш-память (от английского cache – тайник) .

- При обращении процессора к оперативной памяти для считывания в кэш-память передается блок информации, содержащий нужное слово. При этом происходит опережающая выборка, так как высока вероятность, что ближайшие обращения будут происходить к словам этого же блока, уже размещенном в кэш-памяти. Это приводит к значительному уменьшению среднего времени, затрачиваемого на выборку данных.

Обычно используют два типа кэш-памяти:

- Кэш с запоминанием новой информации одновременно в кэш и в оперативную память («сквозное запоминание» или по-английски store - through )

- Кэш с запоминанием новой информации только в кэш-память и копированием ее в оперативную память только при передаче в другие устройства или при вытеснении из кэш ( store - in - cache ).

Повышение производительности компьютерной системы

- Увеличение быстродействия компонентов компьютера (повышение тактовой частоты)

- Увеличение разрядности процессора

- Увеличение количества программно-доступных регистров (сверхоперативной памяти) (уменьшение числа обращений к ОЗУ)

- Применение сверхоперативной кэш-памяти, буферизация, согласование производительности устройств памяти с разным быстродействием

Два фундаментальных принципа повышения производительности

Для задач, решение которых состоит в выполнении множества подзадач, набора более элементарных операций

- Распараллеливание

- Конвейеризация

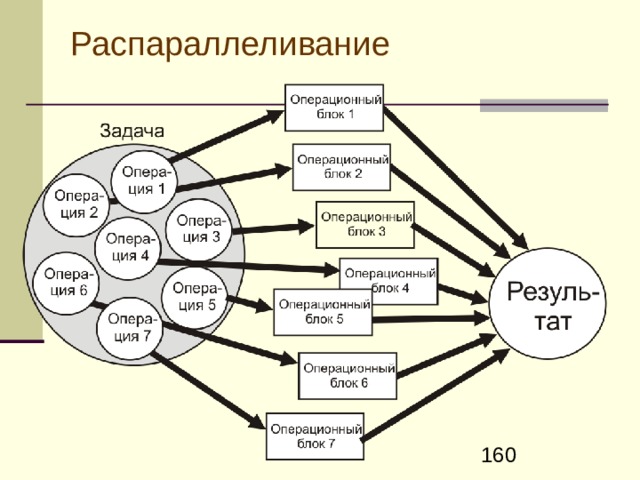

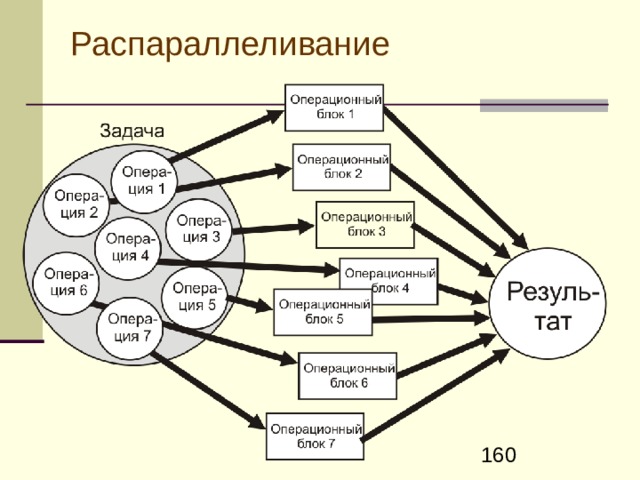

Распараллеливание

- Одновременное выполнение составляющих задачу операций множеством операционных устройств

Распараллеливание

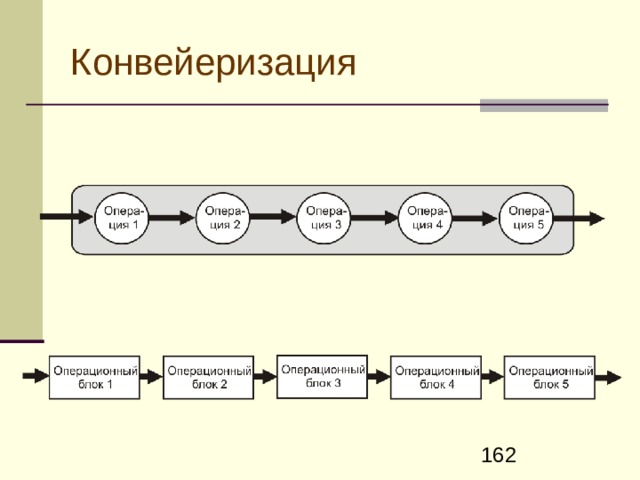

Конвейеризация

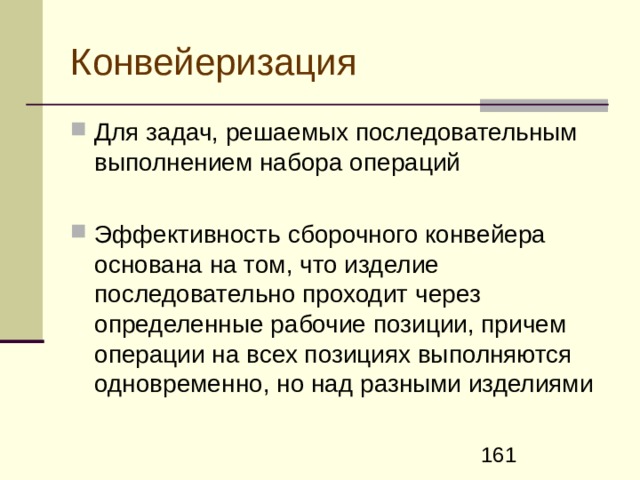

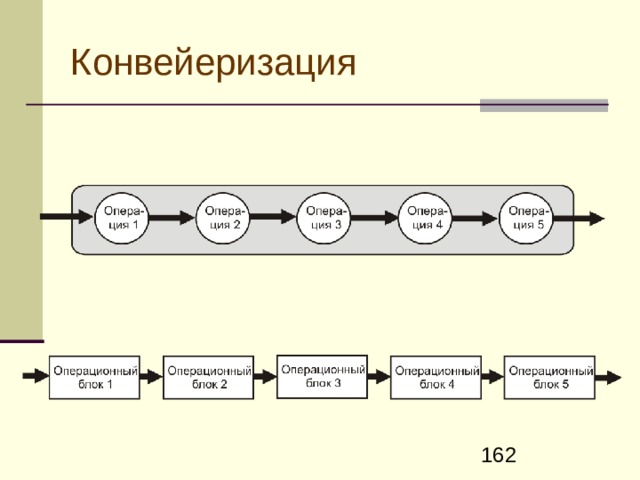

- Для задач, решаемых последовательным выполнением набора операций

- Эффективность сборочного конвейера основана на том, что изделие последовательно проходит через определенные рабочие позиции, причем операции на всех позициях выполняются одновременно, но над разными изделиями

Конвейеризация

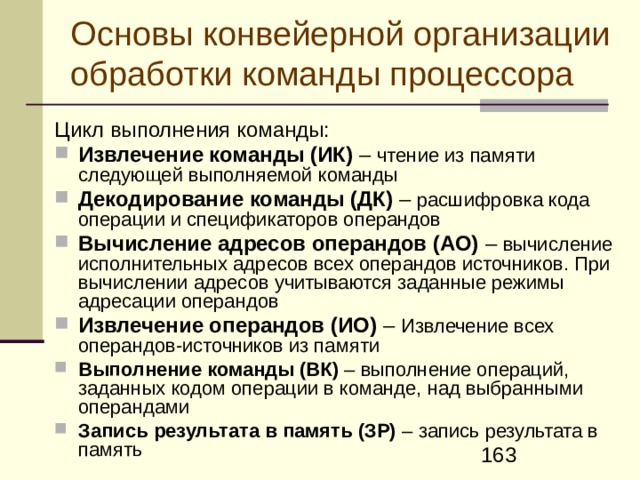

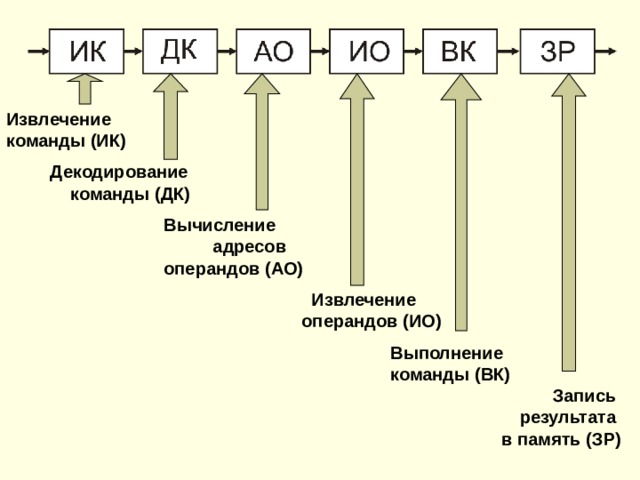

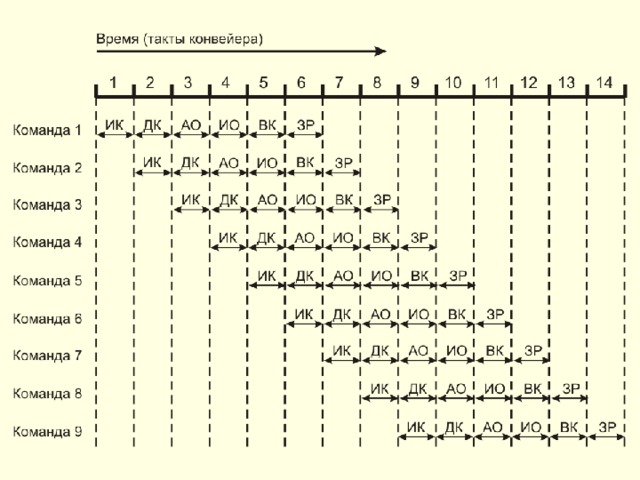

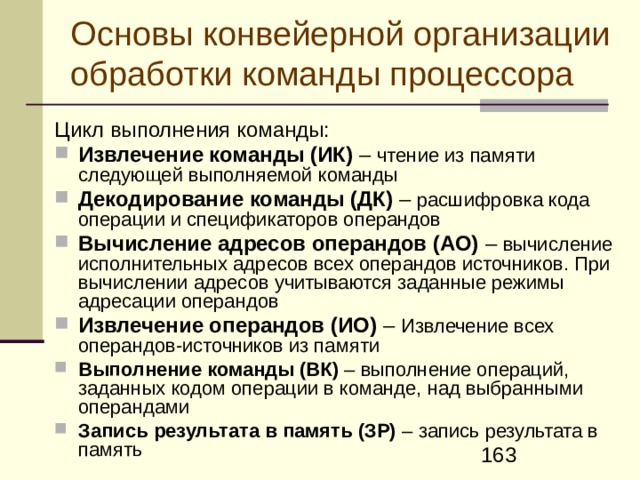

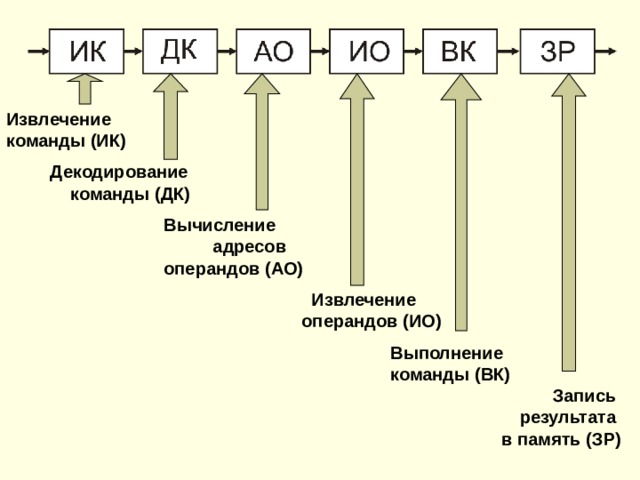

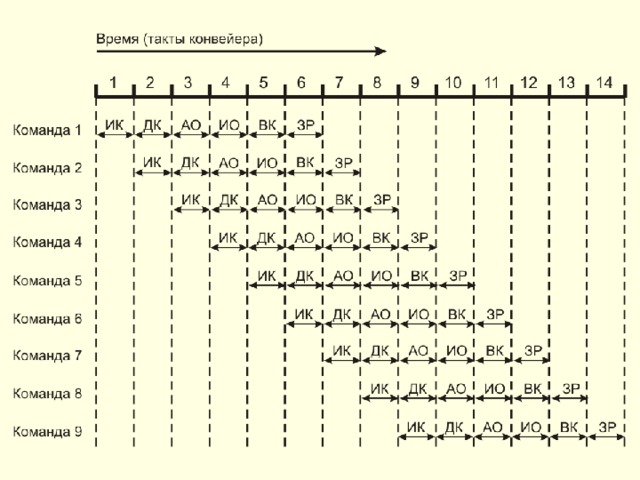

Основы конвейерной организации обработки команды процессора

Цикл выполнения команды:

- Извлечение команды (ИК) – чтение из памяти следующей выполняемой команды

- Декодирование команды (ДК) – расшифровка кода операции и спецификаторов операндов

- Вычисление адресов операндов (АО) – вычисление исполнительных адресов всех операндов источников. При вычислении адресов учитываются заданные режимы адресации операндов

- Извлечение операндов (ИО) – Извлечение всех операндов-источников из памяти

- Выполнение команды (ВК) – выполнение операций, заданных кодом операции в команде, над выбранными операндами

- Запись результата в память (ЗР) – запись результата в память

Извлечение

команды (ИК)

Декодирование

команды (ДК)

Вычисление

адресов

операндов (АО)

Извлечение

операндов (ИО)

Выполнение

команды (ВК)

Запись

результата

в память (ЗР)

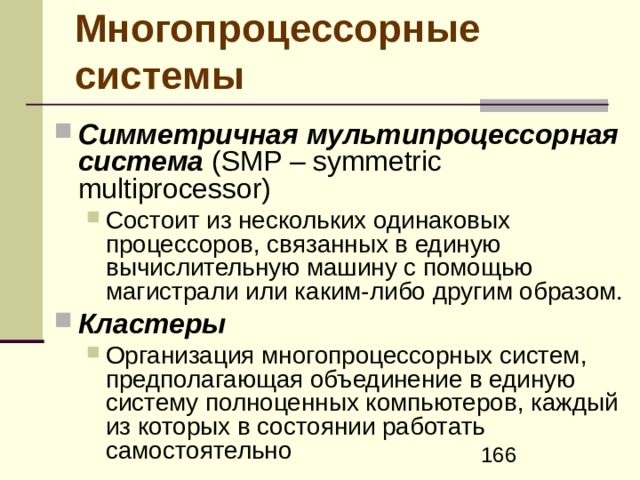

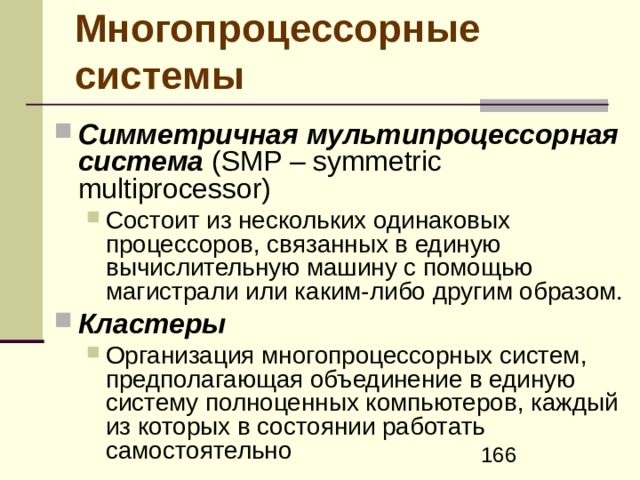

Многопроцессорные системы

- Симметричная мультипроцессорная система ( SMP – symmetric multiprocessor)

- Состоит из нескольких одинаковых процессоров, связанных в единую вычислительную машину с помощью магистрали или каким-либо другим образом.

- Состоит из нескольких одинаковых процессоров, связанных в единую вычислительную машину с помощью магистрали или каким-либо другим образом.

- Организация многопроцессорных систем, предполагающая объединение в единую систему полноценных компьютеров, каждый из которых в состоянии работать самостоятельно

- Организация многопроцессорных систем, предполагающая объединение в единую систему полноценных компьютеров, каждый из которых в состоянии работать самостоятельно

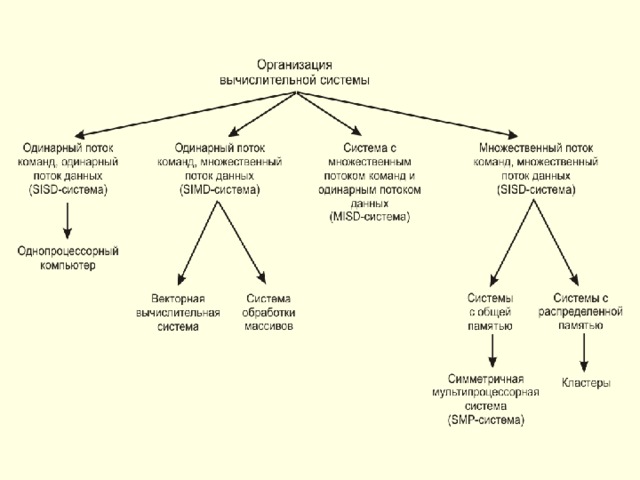

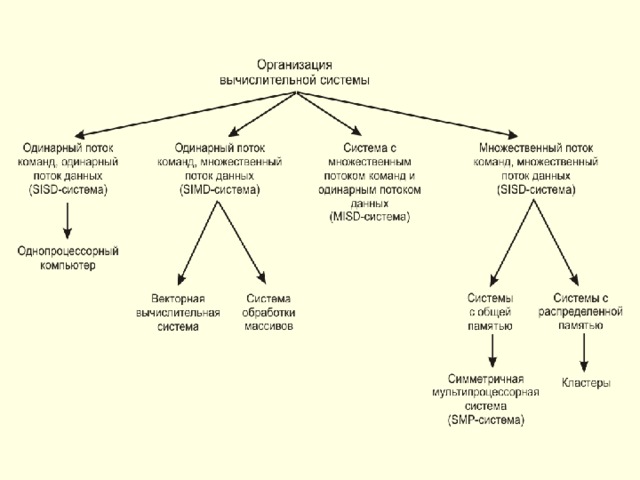

Классификация вычислительных систем

- Предложена М.Флинном ( M . I . Flynn)

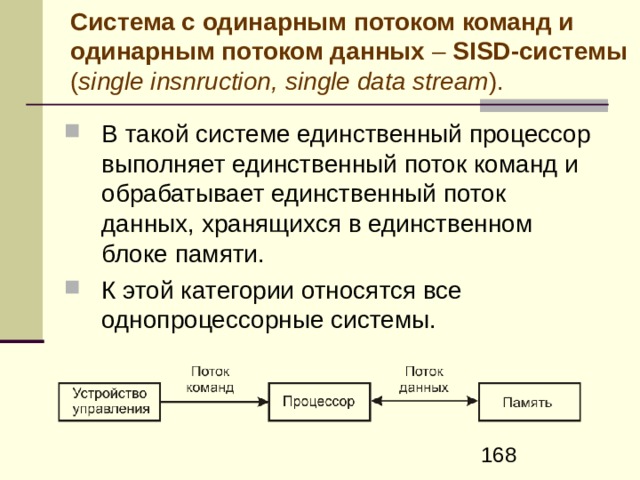

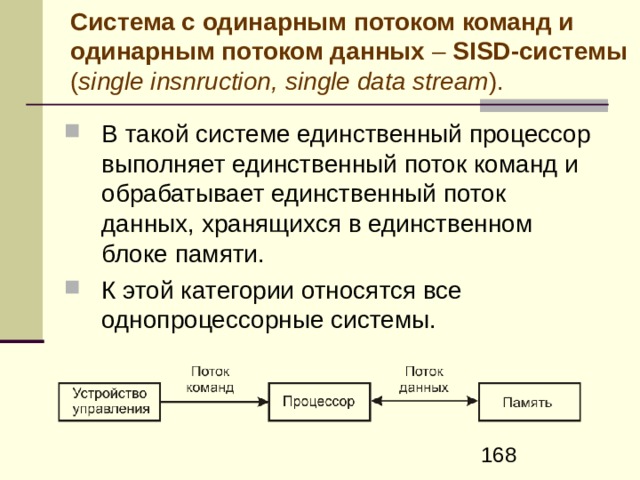

Система с одинарным потоком команд и одинарным потоком данных – SISD -системы ( single insnruction , single data stream ) .

- В такой системе единственный процессор выполняет единственный поток команд и обрабатывает единственный поток данных, хранящихся в единственном блоке памяти.

- К этой категории относятся все однопроцессорные системы.

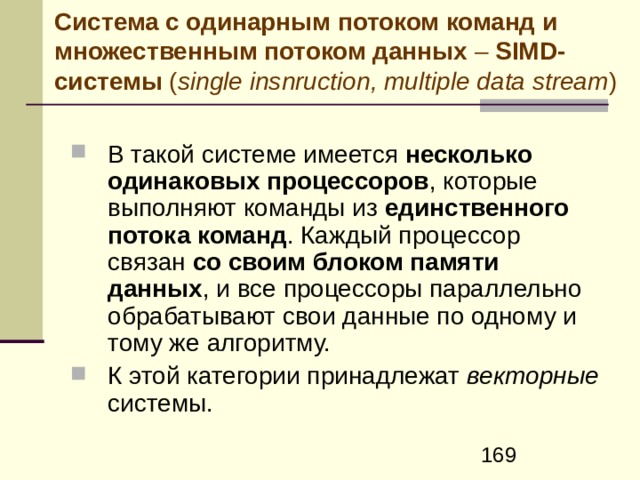

Система с одинарным потоком команд и множественным потоком данных – SIMD -системы ( single insnruction , multiple data stream )

- В такой системе имеется несколько одинаковых процессоров , которые выполняют команды из единственного потока команд . Каждый процессор связан со своим блоком памяти данных , и все процессоры параллельно обрабатывают свои данные по одному и тому же алгоритму.

- К этой категории принадлежат векторные системы.

Система с одинарным потоком команд и множественным потоком данных – SIMD -системы ( single insnruction , multiple data stream )

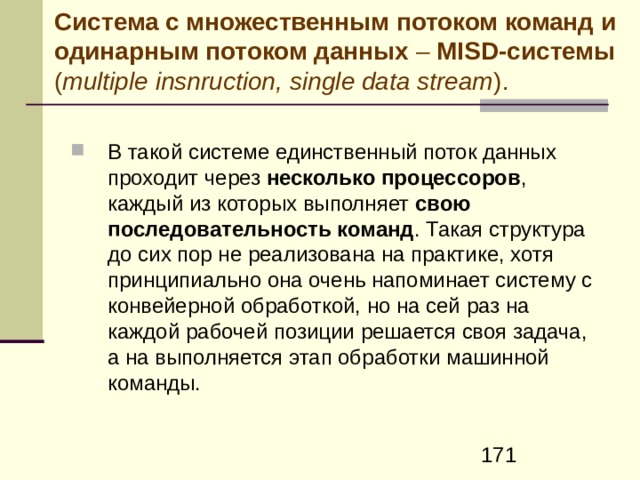

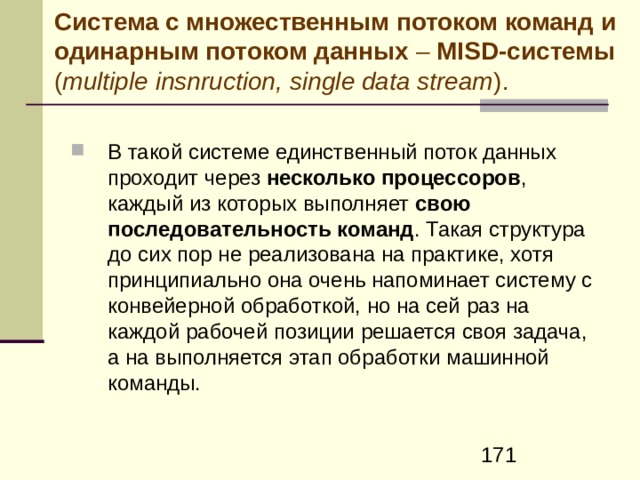

Система с множественным потоком команд и одинарным потоком данных – MISD -системы ( multiple insnruction , single data stream ) .

- В такой системе единственный поток данных проходит через несколько процессоров , каждый из которых выполняет свою последовательность команд . Такая структура до сих пор не реализована на практике, хотя принципиально она очень напоминает систему с конвейерной обработкой, но на сей раз на каждой рабочей позиции решается своя задача, а на выполняется этап обработки машинной команды.

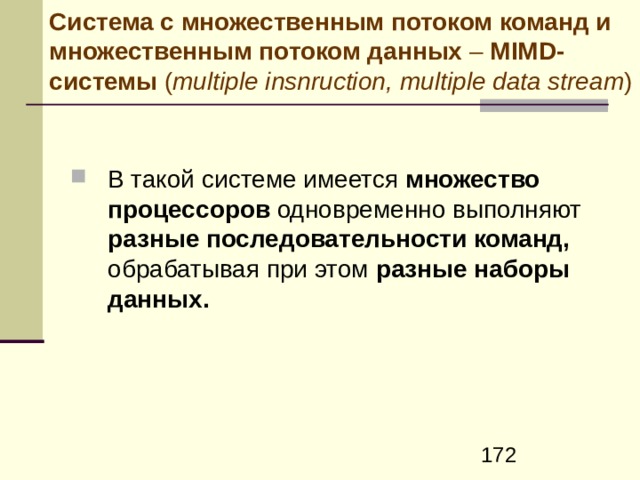

Система с множественным потоком команд и множественным потоком данных – MIMD -системы ( multiple insnruction , multiple data stream )

- В такой системе имеется множество процессоров одновременно выполняют разные последовательности команд, обрабатывая при этом разные наборы данных.

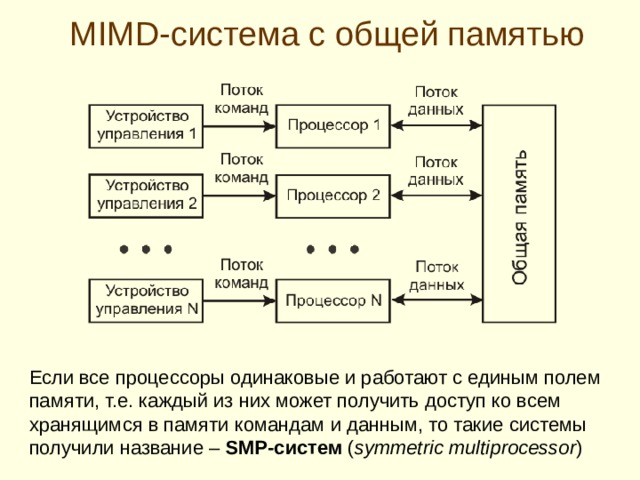

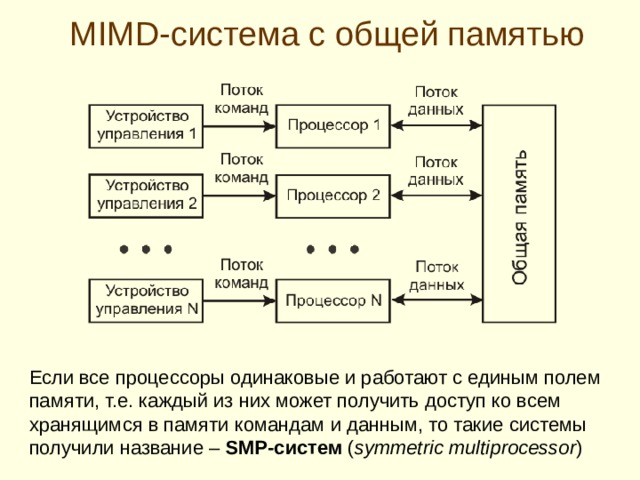

MIMD -система с общей памятью

Если все процессоры одинаковые и работают с единым полем памяти, т.е. каждый из них может получить доступ ко всем хранящимся в памяти командам и данным, то такие системы получили название – SMP -систем ( symmetric multiprocessor )

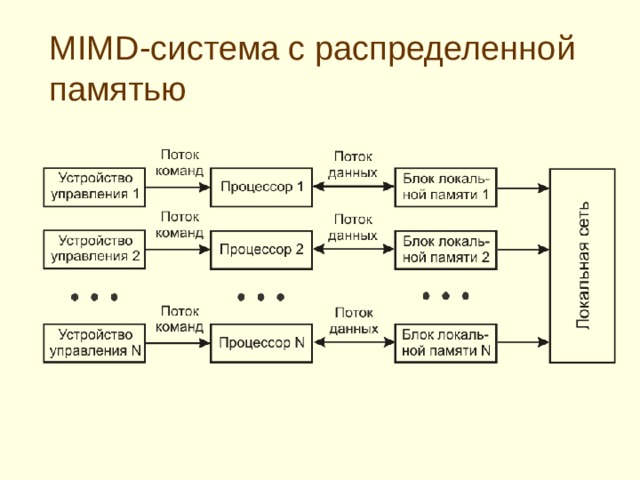

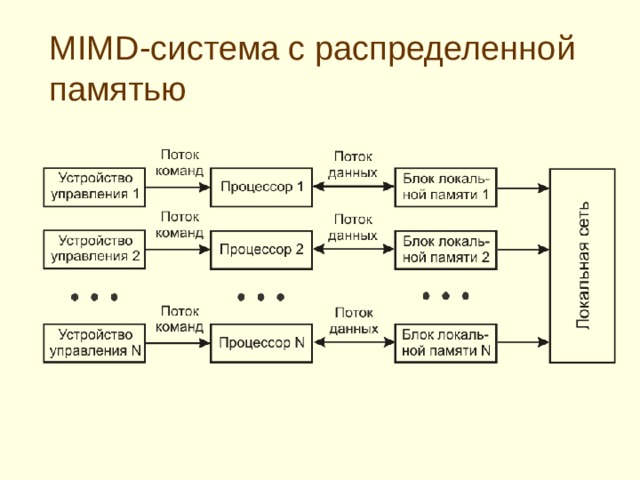

MIMD -система с распределенной памятью

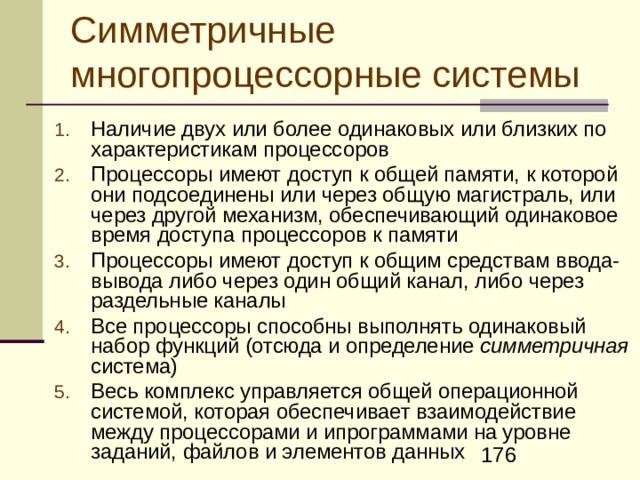

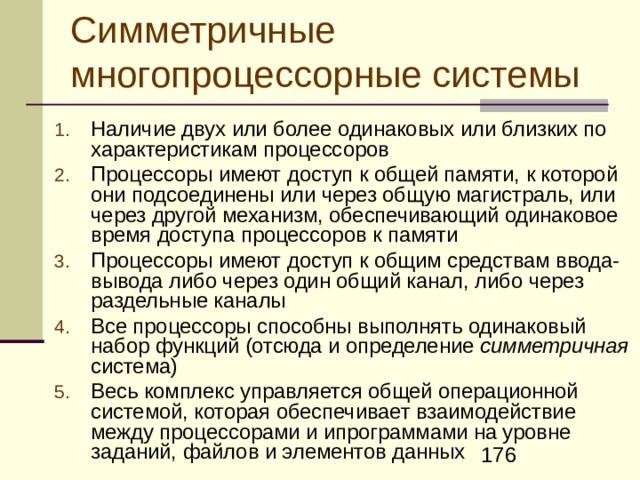

Симметричные многопроцессорные системы

- Наличие двух или более одинаковых или близких по характеристикам процессоров

- Процессоры имеют доступ к общей памяти, к которой они подсоединены или через общую магистраль, или через другой механизм, обеспечивающий одинаковое время доступа процессоров к памяти

- Процессоры имеют доступ к общим средствам ввода-вывода либо через один общий канал, либо через раздельные каналы

- Все процессоры способны выполнять одинаковый набор функций (отсюда и определение симметричная система)

- Весь комплекс управляется общей операционной системой, которая обеспечивает взаимодействие между процессорами и ипрограммами на уровне заданий, файлов и элементов данных

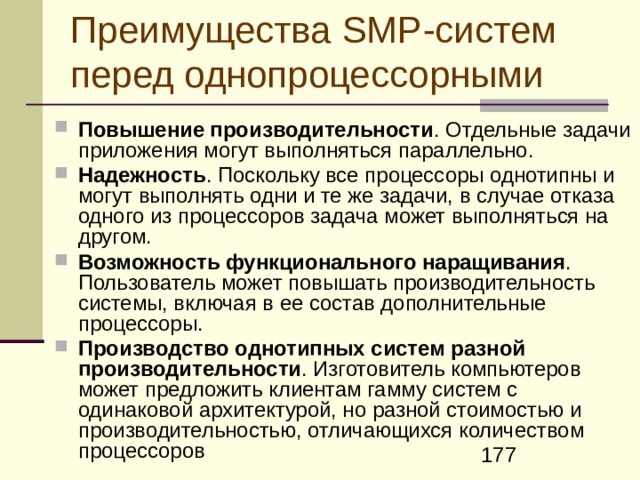

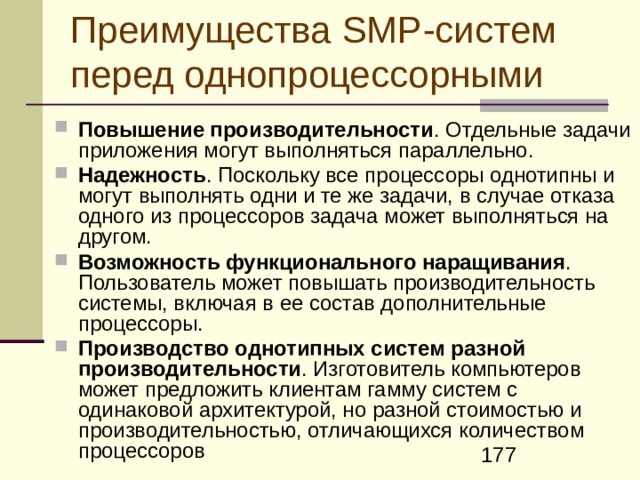

Преимущества SMP -систем перед однопроцессорными

- Повышение производительности . Отдельные задачи приложения могут выполняться параллельно.

- Надежность . Поскольку все процессоры однотипны и могут выполнять одни и те же задачи, в случае отказа одного из процессоров задача может выполняться на другом.

- Возможность функционального наращивания . Пользователь может повышать производительность системы, включая в ее состав дополнительные процессоры.

- Производство однотипных систем разной производительности . Изготовитель компьютеров может предложить клиентам гамму систем с одинаковой архитектурой, но разной стоимостью и производительностью, отличающихся количеством процессоров

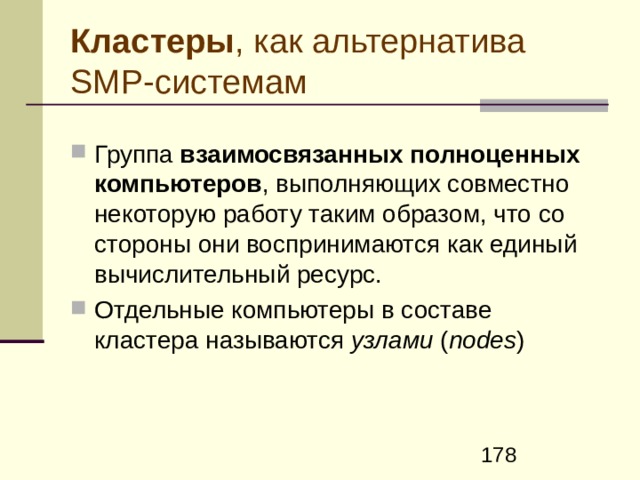

Кластеры , как альтернатива SMP -системам

- Группа взаимосвязанных полноценных компьютеров , выполняющих совместно некоторую работу таким образом, что со стороны они воспринимаются как единый вычислительный ресурс.

- Отдельные компьютеры в составе кластера называются узлами ( nodes )

Преимущества кластеров

- Абсолютная масштабируемость . Включение в кластера любого числа компьютеров.

- Наращивание в процессе эксплуатации . В процессе эксплуатации можно добавлять новые узлы.

- Высокая надежность . Поскольку каждый узел является самодостаточным компьютеров, отказ одного узла не приводит потере работоспособности всего комплекса.

- Снижение соотношения цена/производительность . При построении кластера могут использоваться компьютеры массового производства, т.е. более дешевые.