Просмотр содержимого документа

«МК AVR Семейства Mega»

ДЕПАРТАМЕНТ ОБРАЗОВАНИЯ, НАУКИ И МОЛОДЕЖНОЙ ПОЛИТИКИ ВОРОНЕЖСКОЙ ОБЛАСТИ ГБПОУ ВО «Богучарский многопрофильный колледж»

Микроконтроллеры AVR Семейства Mega

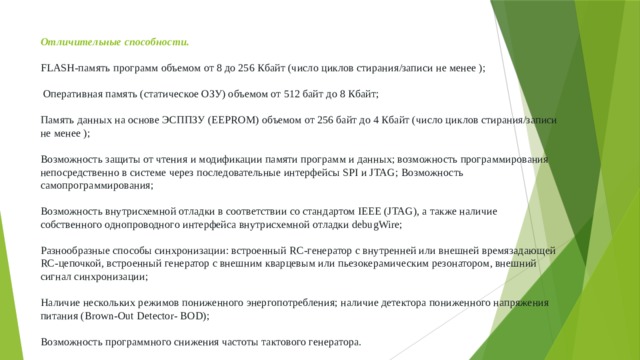

Отличительные способности. FLASH-память программ объемом от 8 до 256 Кбайт (число циклов стирания/записи не менее ); Оперативная память (статическое ОЗУ) объемом от 512 байт до 8 Кбайт; Память данных на основе ЭСППЗУ (EEPROM) объемом от 256 байт до 4 Кбайт (число циклов стирания/записи не менее ); Возможность защиты от чтения и модификации памяти программ и данных; возможность программирования непосредственно в системе через последовательные интерфейсы SPI и JTAG; Возможность самопрограммирования; Возможность внутрисхемной отладки в соответствии со стандартом IEEE (JTAG), а также наличие собственного однопроводного интерфейса внутрисхемной отладки debugWire; Разнообразные способы синхронизации: встроенный RС-генератор с внутренней или внешней времязадающей RС-цепочкой, встроенный генератор с внешним кварцевым или пьезокерамическим резонатором, внешний сигнал синхронизации; Наличие нескольких режимов пониженного энергопотребления; наличие детектора пониженного напряжения питания (Brown-Out Detector- BOD); Возможность программного снижения частоты тактового генератора.

Характеристики процессора. Полностью статическая архитектура, минимальная тактовая частота равна нулю; Арифметико-логическое устройство (АЛУ) подключено непосредственно к регистрам (общего назначения 32 регистра); Большинство команд выполняются за один период тактового сигнала; векторная система прерываний, поддержка очереди прерываний; Большое число источников прерываний (до 45 внутренних и до 32 внешних); наличие аппаратного умножителя.

Характеристики подсистемы ввода/вывода. Программное конфигурирование и выбор портов ввода/вывода; Выводы могут быть запрограммированы как входные или как выходные независимо друг от друга; Входные буферы с триггером Шмитта на всех выводах; Имеется возможность полного отключения цифрового порта ввода/вывода от физического вывода микросхемы; На всех входах имеются индивидуально отключаемые внутренние подтягивающие резисторы сопротивлением кОм.

Периферийные устройства. Один или два 8-битных таймера/счетчика; От одного до четырех 16-битных таймеров/счетчиков; Сторожевой таймер; Одно- и двухканальные генераторы 8-битного ШИМ-сигнала (один из режимов работы 8-битных таймеров/счетчиков); Двух- и трехканальные генераторы ШИМ-сигнала регулируемой разрядности (один из режимов работы 16-битных таймеров/счетчиков). Разрешение формируемого сигнала может составлять от 1 до 16 бит; Аналоговый компаратор; Многоканальный 10-битный АЦП последовательного приближения; последовательный синхронный интерфейс SPI; Последовательный двухпроводный интерфейс TWI (полный аналог интерфейса I 2 С).

Особенности микроконтроллера ATmega128. 7 портов ввода/вывода (порты A...F 8-битные, порт G 5-битный); Возможность подключения внешнего ОЗУ; Два 8-битных (ТО, Т2) и два 16-битных (T1, T3) таймера/счетчика; 8 каналов ШИМ; Два модуля USART и по одному модулю SPI и TWI; 8-канальный 10-битный АЦП; Интерфейс JTAG.

X-регистр, Y-регистр и Z-регистр.

Основные возможности работы с внешней памятью. Подключение двух микросхем внешней памяти разного размера и с различной скоростью работы Определение двух секторов в адресном пространстве памяти, соответствующих разным микросхемам Определение различных временных задержек для различных секторов адресного пространства Использование части линий порта С для адресации внешней памяти, оставшихся линий – для стандартного ввода/вывода