Урок 25

ЛОГ И ЧЕСКИЕ ЭЛЕМЕНТЫ

Логический элемент – это такая схема, у которой несколько входов и один выход. Каждому состоянию сигналов на входах, соответствует определенный сигнал на выходе. Схема выполняет какую-либо логическую операцию (операции) над входными данными, заданными в виде уровней напряжения, и возвращает результат операции в виде выходного уровня напряжения.

Для того, чтобы понять как логический элемент работает, нужно нарисовать таблицу, в которой будут перечислены состояния на выходе при любой комбинации входных сигналов. Такая таблица называется таблицей истинности и ли переключательной таблицей .

- Логические элементы предназначены для реализации логических функций и являются одним из наиболее распространенных типов цифровых устройств, имеющих как самостоятельное применение, так и входящих в состав более сложных схем, выполненных на их основе, например, триггеров, регистров, счетчиков, распределителей, сумматоров, дешифраторо

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

Элементарными логическими функциями являются: логическое сложение (дизъюнкция), логическое умножение (конъюнкция), логическое отрицание (инверсия).

Аналитические формы записи функций позволяют получить основные законы алгебры логики отдельно для операций логического умножение и сложения (И и ИЛИ).

Элемент «И» (AND) – конъюнктор

Единица на выходе элемента «И» возникает только тогда, когда на оба входа поданы единицы. Это объясняет название элемента: единицы должны быть И на одном, И на другом входе.

Элемент «ИЛИ» (OR) – дизъюнктор

На выходе возникает единица, когда на один ИЛИ на другой ИЛИ на оба сразу входа подана единица.

Элемент «И-НЕ» ( NAND)

Элемент «ИЛИ-НЕ» ( NOR)

Элемент «НЕ» (NOT) - инвертор

Элемент «Исключающее ИЛИ» ( XOR)

На выходе единицы, когда на входах разные сигналы: на одном – 1, на другом – 0. Операция, которую он выполняет, часто называют «сложение по модулю 2».

Микросхемы, внутри которых содержатся цифровые элементы. Около выводов элементов обозначены номера соответствующих выводов микросхемы. Все микросхемы, перечисленные здесь, имеют 14 выводов. Питание подается на выводы 7 ( gnd ) и 14 (+).

U пор ; VD1 открыт→ I R ≠ 0 U вх1 U пор → I R ≈ U вх /R U вых ≠0; U вых ≅ U вх - U пор Напряжение на выходе схемы будет равно E ( F = 1), если хотя бы на один из входов будет подан единичный сигнал. X1 0 X2 Y 0 0 1 0 1 1 1 0 1 1 1 " width="640"

U пор ; VD1 открыт→ I R ≠ 0 U вх1 U пор → I R ≈ U вх /R U вых ≠0; U вых ≅ U вх - U пор Напряжение на выходе схемы будет равно E ( F = 1), если хотя бы на один из входов будет подан единичный сигнал. X1 0 X2 Y 0 0 1 0 1 1 1 0 1 1 1 " width="640"

ПРИНЦИП ПОСТРОЕНИЯ ЛЭ НА ОСНОВЕ ПОЛУПРОВОДНИКОВЫХ ДИОДОВ

Операция ИЛИ.

1. U вх1 = U вх2 =0

Диоды VD 1 и VD 2 закрыты, ток I R =0, U вых =0.

2. U вх1 ≠0 U вх1 U пор ; VD1 открыт→ I R ≠ 0

U вх1 U пор → I R ≈ U вх /R

U вых ≠0; U вых ≅ U вх - U пор

Напряжение на выходе схемы будет равно E ( F = 1), если хотя бы на один из входов будет подан единичный сигнал.

X1

0

X2

Y

0

0

1

0

1

1

1

0

1

1

1

Напряжение на выходе U вых ~ Е ( F = 1) будет только в том случае, если все диоды будут закрыты, т. е. на всех входах будет потенциал Е (логическая 1).

В противном случае открывшийся диод шунтирует нагрузку и U вых = 0.

Операция И

I R1 = ( U п - U д1 ) /R1≈ U п /R1

U вых ≈ U д1 =0

VD1 и VD2 закрыты

U вых = R2/(R1+R2)* U п

X1

0

X2

0

0

Y

1

0

1

1

0

0

0

1

1

ДТЛ

Диодно–транзисторная логика (ДТЛ) представляет собой сочетание диодных логических ячеек с транзисторным инвертором.

Базовым логическим элементом всех серий ДТЛ является элемент И–НЕ, реализующий операцию логического умножения с отрицанием.

- Входные диоды VD1…VD3 и резистор R1 образуют входную логическую схему, выполняющую в положительной логике операцию И. Инвертор на транзисторе VТ1 выполняет логическую операцию НЕ, усиливает и формирует сигналы на выходе до стандартного уровня.

- Смещающие диоды VD4 и VD5 предназначены для увеличения порога запирания и помехоустойчивости схемы в закрытом состоянии, а резистор R2 и U 2ип обеспечивают оптимальную величину тока этих диодов. Диоды VD1…VD3 должны обладать минимальным сопротивлением в проводящем состоянии; высоким (максимальным) обратным напряжением; малой емкостью и малым временем восстановления обратного сопротивления.

ТТЛ

- Принципиальная электрическая схема, условное обозначение, временные диаграммы базового логического элемента серий ТТЛ приведены на рис 9.16. Базовый логический элемент ТТЛ выполняет операцию И–НЕ. Схема базового элемента ТТЛ состоит из двух частей. Входная часть реализует логическую функцию И с помощью VТ1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VТ2…VТ4.

Базовые элементы различных серий ТТЛ различаются только инверторами, которые должны улучшать переходные характеристики, повышать помехоустойчивость и нагрузочную способность, потреблять небольшую мощность.

Для уменьшения входных токов транзистор VТ1 должен обладать малым коэффициентом передачи тока базы в инверсном режиме h i э 21 ≈0,005…0,05 .

Логические элементы со сложным инвертором потребляют большую мощность, занимают большую площадь кристалла, поэтому на их основе изготавливаются цифровые микросхемы малой и средней степени интеграции.

Быстродействие логических элементов различных серий ТТЛ можно повысить двумя путями:

– уменьшая сопротивление резисторов и паразитные емкости;

– обеспечивая работу транзисторов в активном, т.е. ненасыщенном режиме, при котором отсутствует накопление и рассасывание носителей в базах транзисторов. Оба эти способа повышения быстродействия нашли практическое применение.

БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ - ТТЛ

Наибольшее распро-странение получили логи-ческие элементы на осно - ве ТТЛ ( Транзисторно-Транзисторная Логика ) структур

+Ек

R4

R2

R1

VT1

VT3

VT2

VD

X1

X2

Y

X3

VT4

X4

R3

Многоэмиттерный транзистор ( МЭТ ) VT1 совместно с резистором R1 образует логическую схему « И ». На трех транзисторах ( VT2...VT4 ) реализован инвертор ( по схеме Дарлингтона). Коллекторной нагрузкой инвертора является резистор R2 . Для уменьшения времени перезаряда паразитных конденсаторов нагрузки ( Сн ) через резистор R2 при закрывании составного транзистора VT2 и VT4 введен дополнительный эмиттерный повторитель VT3 .

Кроме положительного эффекта (увеличение примерно в h 21 раз тока перезарядки паразитных конденсаторов нагрузки) введение эмиттерного повторителя породило ряд проблем. При открытом транзисторе VT3 должны быть закрыты транзисторы VT2 и VT4 . Однако время открывания транзистора VT3 значительно меньше времени закрывания VT2, VT4 (с учетом времени рассасывания носителей в базе). Поэтому при открывании эмиттерного повторителя VT3 транзистор VT4 находится еще в стадии рассасывания. Через два открытых транзистора VT3 и VT4 течет очень большой сквозной ток от источника питания. Для ограничения этого тока введен дополнительный резистор R4 .

Дополнительно введен также диод VD для надежного запирания эмиттерного повторителя VT3 при открывании транзисторов VT2 и VT4. У транзисторов VT2, VT4, находящихся в режиме насыщения, напряжение Uбэ = 0,7 В , а напряжение Uкэ = 0,2 В . При этом напряжение на базе VT3 (относительно общего провода) равно :

Uбэ VT4 + Uкэ VT2 = 0,9 В.

А напряжение на эмиттере VT3 (относительно общего провода при отсутствии диода VD ) равно:

Uкэ VT4=0,2 В.

Из этого следует, что ( при отсутствии диода ) напряжение между эмиттером и базой VT3 не может быть меньше 0,7 В , т.е. транзистор VT3 невозможно закрыть. При введении дополнительного диода VD это напряжение ( 0,7 В ) разделяется между переходом эмиттер-база VT3 и диодом. П ри напряжении 0,35 В переход эмиттер-база и кремниевый диод находятся в ПРЕДПОРОГОВОМ ( нетокопроводящем ) состоянии.

При закрывании транзисторов VT2 и VT4 открывается эмиттерный повторитель VT3. Но напряжение на выходе инвертора будет меньше напряжения источника питаня (обычно Ек = 5 Вольт ) на величину падения напряжения на переходе эмиттер-база VT3 и на диоде VD. Поэтому высокому (единичному) логическому уровню на выходе инвертора соответствует напряжение :

U 1вых = Ек – ( I б * R 2) – (2 * 0,7) ≈ 3,5В

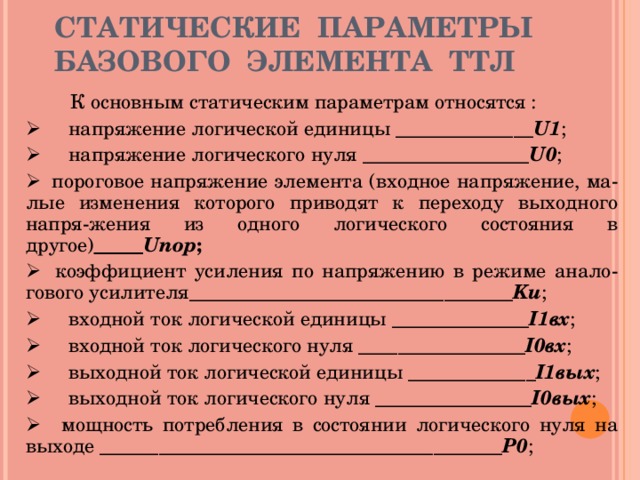

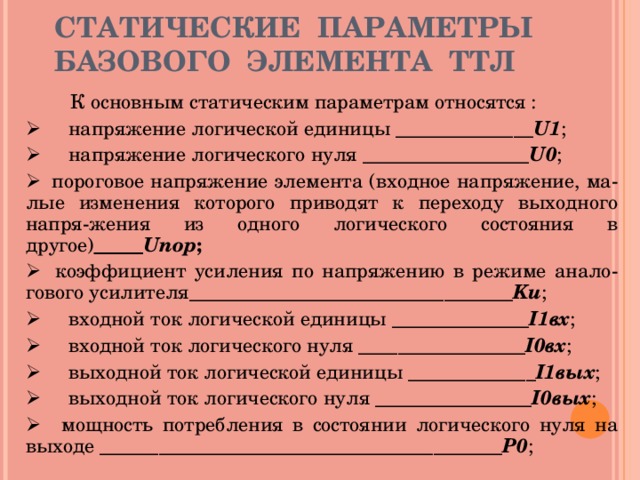

СТАТИЧЕСКИЕ ПАРАМЕТРЫ БАЗОВОГО ЭЛЕМЕНТА ТТЛ

К основным статическим параметрам относятся :

напряжение логической единицы ______________ U1 ;

напряжение логического нуля _________________ U0 ;

пороговое напряжение элемента (входное напряжение, ма - лые изменения которого приводят к переходу выходного напря - жения из одного логического состояния в другое) _____ Uпор ;

коэффициент усиления по напряжению в режиме анало - гового усилителя _________________________________ Ku ;

входной ток логической единицы ______________ I1вх ;

входной ток логического нуля _________________ I0вх ;

выходной ток логической единицы _____________ I1вых ;

выходной ток логического нуля ________________ I0вых ;

мощность потребления в состоянии логического нуля на выходе _________________________________________ Р0 ;

мощность потребления в состоянии логической единицы на выходе ___________________________________________ Р1 ;

средняя мощность потребления ______ Рср = (Р0 + Р1) / 2 ;

коэффициент разветвления по выходу (нагрузочная спо - собность) ______________________________________ К (раз).

Основные статические параметры можно определить при анализе входной и передаточной характеристик базового ТТЛ элемента. Некоторые статические параметры задаются в ТУ заводом-изготовителем.

U пор ; VD1 открыт→ I R ≠ 0 U вх1 U пор → I R ≈ U вх /R U вых ≠0; U вых ≅ U вх - U пор Напряжение на выходе схемы будет равно E ( F = 1), если хотя бы на один из входов будет подан единичный сигнал. X1 0 X2 Y 0 0 1 0 1 1 1 0 1 1 1 " width="640"

U пор ; VD1 открыт→ I R ≠ 0 U вх1 U пор → I R ≈ U вх /R U вых ≠0; U вых ≅ U вх - U пор Напряжение на выходе схемы будет равно E ( F = 1), если хотя бы на один из входов будет подан единичный сигнал. X1 0 X2 Y 0 0 1 0 1 1 1 0 1 1 1 " width="640"